Part Number: DP83867IR

Tool/software:

Hi Expert,

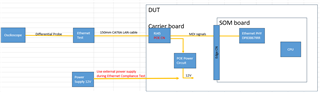

Our customer is currently doing Ethernet Compliance testing and has had some failures

We are referring to the following application note:

https://www.ti.com/lit/an/snla239c/snla239c.pdf

Failures:

10base:

- MAU Int: The signal level is small, so the mask hits and it fails

- MAU Int Inverted: The signal level is small, so the mask hits and it fails

- Differential Voltage: The signal level is small, so it fails

100base : All items are Passed

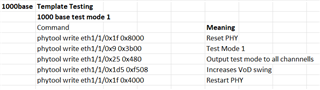

1000base

- Template Test Point F: The rising part of the signal waveform is hit by the mask

- Template Test Point H: The falling part of the signal waveform is hit by the mask

Question:

Q1: 10base: Are there any setting commands/registers to increase the signal level?

Q2: 1000base: Are there any commands/registers to adjust the Rise/Fall of the signal waveform?

Please refer to the attached excel file.

Thanks,

Huy