Other Parts Discussed in Thread: ALP

Tool/software:

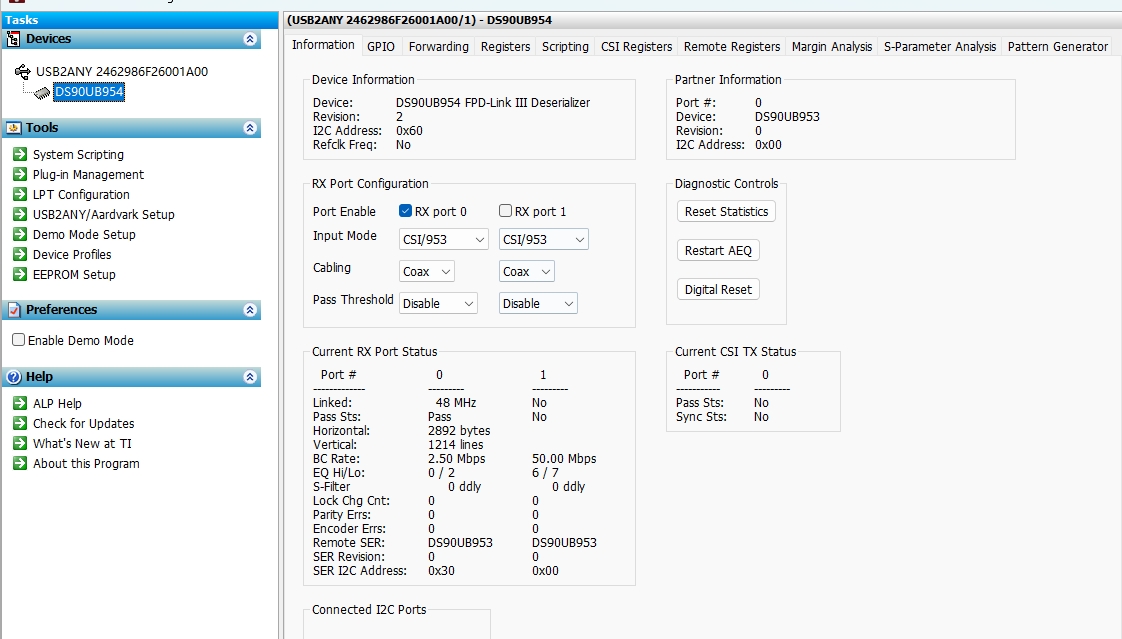

高通845芯片的linux系统,摄像头驱动为软件i2c操作的,不用954和953时可出图像。

现在添加了954和953连接摄像头后,i2c配置完954,953后可访问摄像头I2C,但是运行摄像头驱动软件后,显示SOF freeze。

[ 1012.459078] CAM_INFO: CAM-SENSOR: cam_sensor_driver_cmd: 823 Probe success,slot:0,slave_addr:0x6c,sensor_id:0x5803

[ 1012.459325] CAM_INFO: CAM-SENSOR: cam_sensor_driver_cmd: 896 CAM_ACQUIRE_DEV Success, sensor_id:0x5803,sensor_slave_addr:0x6c

[ 1017.698105] CAM_ERR: CAM-CRM: __cam_req_mgr_process_sof_freeze: 1168 SOF freeze for session 11403776 link 0x330104

[ 1017.698151] CAM_INFO: CAM-ISP: cam_ife_csid_sof_irq_debug: 2683 SOF freeze: CSID SOF irq enabled