Tool/software:

Hello,

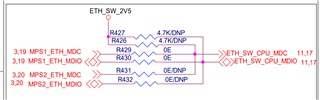

I am working on a custom board that uses the Zynq UltraScale+ MPSoC and the DP83867 PHY for Ethernet communication in SGMII mode. However, I am encountering issues where the PHY is not being properly detected, and the Ethernet link is not established. Below are the details of my setup, observations, and troubleshooting steps:

Setup Details:

- PHY: Texas Instruments DP83867 configured in SGMII mode.

- Processor: Zynq UltraScale+ MPSoC.

Software Details:

- Driver: TI DP83867 PHY driver enabled in Linux kernel (PetaLinux environment).

- Device Tree Configuration: &gem0 {

status = "okay";

phy-mode = "sgmii";

phy-handle = <&phy0>;

mdio {

phy0: ethernet-phy@2 {

compatible = "ti,dp83867";

reg = <2>; // PHY address

};

};

};

- Linux Kernel Version: PetaLinux 2020.1.

Observations:

-

PHY Detection:

dmesgshows the PHY being detected as a "Generic PHY" instead of the TI DP83867-

No Ethernet Link:Using

ethtool, the link status is reported as down -

Ping Fails:The Ethernet interface does not respond to

pingrequests, and no packets are receivedTroubleshooting Steps Taken:

- Verified the hardware strap configuration.

- Confirmed that the DP83867 driver is enabled in the kernel configuration.

- Verified the device tree configuration matches the hardware strap settings

- I have attSMDC_TEST_JIG.pdfached my schematic and test baord pdf files .