Tool/software:

Hello,

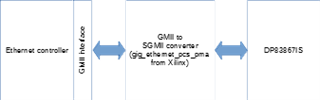

I am trying to put the DP83867ISRGZ phy on the VCU118 board in loopback and send and recieve data from the MAC(with an sgmii adapter interface) in my FPGA design, for a throughput analysis exercise. From the software test I am doing, I see that the MAC is not sending or recieving any data.

The phy digital loopback configuration I did is as follows

Write register 0x00FE with value 0xE720

Write register 0x0 with value 0x0140

Write register 0x0010 with value 0x5028

Write register 0x0016 with value 0x0004

Write register 0x001F with value 0x4000

To sanity check the PHY, I tried some PRBS tests as below

Write register 0x0016 0xF004

Write register 0x0072 0x0201

Read register 0x0071 : Value recieved : 0x8405

Read register 0x0072 : Value recieved : 0x200

Read register 0x01a8 : Value recieved : 0x8f6

Read register 0x01a9 : Value recieved : 0x0

From the documentatin, what I understand is that the PRBS test is recieving some data and does not detect any errors.

I am seeing a link up status in the phy registers too.

I am wondering then why my MAC is not able to send and recieving any data.

I have tested with PHY not in loopback and I can send data out. However when I put the phy in digital loopback, I am not able to do that even with the link up status.

Do you have any clue?