Part Number: TDES954

Tool/software:

Hi Hamzeh,

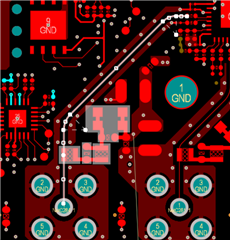

We have following changes to V3Link layout as per below:

- RF trace reference layer changed to Layer-2 instead of Layer-3 which resulted in RF trace width decreased to 5.2mils.

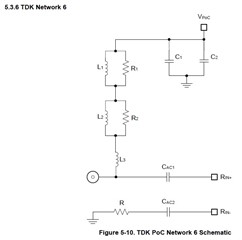

- Changed POC network from TDK Network-5 to TDK Network-6.

We have following queries:

- As shown in below image, we have placed all POC network components on Top layer. Our RF engineer recommends placing all POC components except L3 in the bottom layer to improve RF performance and marginal test results.

- We have kept GND shield trace clearance around the RF trace 3W (15.6mils) far away each side and kept 4W (20.8mils) anti pad at RF TH pin for Fakra connector.

We would like to know your recommendations and inputs here to proceed further.