Part Number: TMDS181

Tool/software:

Hi team,

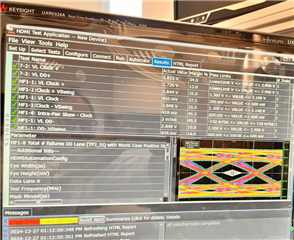

Below are customer's eye pattern test results, which work well with refresh 30 but failed with refresh 60. Do you have any insights on how to optimize it?

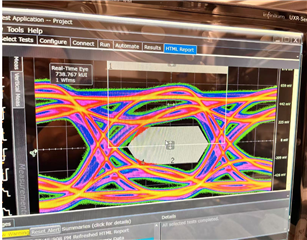

refresh 30:

refresh 60:

Sch:6404.HDMI Re-timer 线路12.24.pdf

Note: In sch, customer used skip wire to connect the SCL_CTL/SDA_CTL to host and configure through I2C. I2C_EN is also enabled after checking.

Support need:

- Could you please help to give some adjustment suggestion to help customer complete the eye pattern test? such as, register modification... I have asked customer try to set to adaptive EQ mode and will post the results to you later.

- It's found that there is a drop on the waveform. Could you please also help to check the reason and how to fix it?

- BTW, do we have any documents on how to configure the re-timer based on the eye pattern test?

Thanks!

BRs,

Rannie