Tool/software:

Hi,

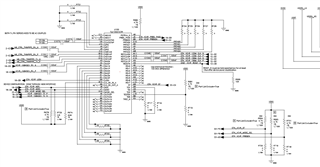

I'm looking for support with the schematic implementation of the TLK10031. I've some questions as to how to connect some of the signals.

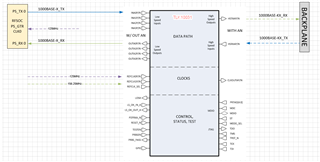

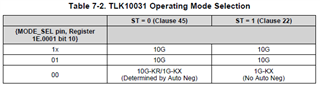

1.- How do I connect the MODE_SEL and the ST pins if we plan to configure the High-Speed port as 1000Base-KX and the low-Speed Port as 1000Base-X

2.- How do I connect the PRBSEN signal?

3.- Do I need to connect the PRTAD0..4 pins to a specific address, tie them all to ground or leave them unconnected?

4.- Is JTAG needed for something else other than boundary scan?

5.- Is there any programming needed for the part of is the programming/configuration done through MDIO?

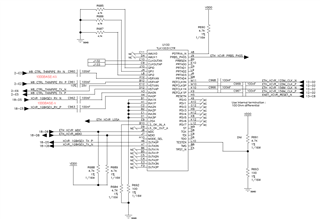

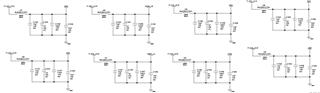

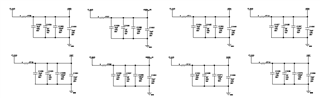

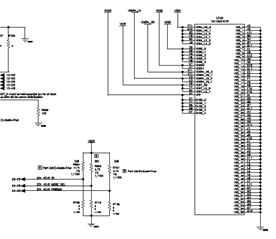

6.- Would you please review the schematic implementation for accuracy.