Part Number: TLK10232

Tool/software:

We have a few more questions regarding the use of TLK10232. These are:

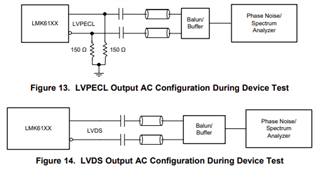

* REFCLK connection

- What are the termination requirements for the REFCLK inputs when using an 156.25MHz LVPECL oscillator as clock source? Is there a reference circuit available. The EVM schematics show a direct connection from the AC coupling capacitors ti the TLK pins.

- How critical is the rise/fall time requirement? It looks not easy to find LVPECL/LVDS oscillators which safely guarantee meeting the maximum value. Are there any oscillator recommendations?

* Additional documentation

The data sheet states in table 8-22 "Refer to TLK10232 Bringup Procedure (a separate document) for more information.". How can we access this separate document?

* XAUI link/bridge not free of errors

On the LS/XAUI side we have the TLK device connected to a NWP (MCHP) on one channel and a 10GPHY (MCHP) on the other channel. In one scenario we have bridged the 2 channels using the internal switch (see my other E2E post). While in general this bridge is working we face the fact that a very small amount of FCS errors being reported by both XAUI link partners (NWP, PHY).

It must be noted that during this test nothing was connected to the HS/KR side.

A register dump of the 0x1E device (VENDOR SPECIFIC) in the XAUI bridge configuration looks like this (PHY side):

reg value description

1Ex0000 0x0610 GLOBAL_CONTROL_1

1Ex0001 0x0b24 CHANNEL_CONTROL_1

1Ex0002 0x831d HS_SERDES_CONTROL_1

1Ex0003 0xa848 HS_SERDES_CONTROL_2

1Ex0004 0x1500 HS_SERDES_CONTROL_3

1Ex0005 0x2000 HS_SERDES_CONTROL_4

1Ex0006 0xf115 LS_SERDES_CONTROL_1

1Ex0007 0x0000 LS_SERDES_CONTROL_2

1Ex0008 0x0000 LS_SERDES_CONTROL_3

1Ex0009 0x0380 HS_OVERLAY_CONTROL

1Ex000A 0x1fff LS_OVERLAY_CONTROL

1Ex000B 0x0d10 LOOPBACK_TP_CONTROL

1Ex000C 0x0371 LS_CONFIG_CONTROL

1Ex000D 0x2f80 CLK_CONTROL

1Ex000E 0x0000 RESET_CONTROL

1Ex000F 0x70af CHANNEL_STATUS_1

1Ex0010 0x0000 HS_ERROR_COUNTER

1Ex0011 0x0000 LS_LN0_ERROR_COUNTER

1Ex0012 0x0000 LS_LN1_ERROR_COUNTER

1Ex0013 0x0000 LS_LN2_ERROR_COUNTER

1Ex0014 0x0000 LS_LN3_ERROR_COUNTER

1Ex0015 0x4146 LS_STATUS_1 (lane0)

1Ex0015 0x4146 LS_STATUS_1 (lane1)

1Ex0015 0x4146 LS_STATUS_1 (lane2)

1Ex0015 0x4146 LS_STATUS_1 (lane3)

1Ex0016 0xf006 HS_STATUS_1

1Ex0017 0x2000 DST_CONTROL_1

1Ex0018 0x0c20 DST_CONTROL_2

1Ex0019 0x2500 DSR_CONTROL_1

1Ex001A 0xac20 DSR_CONTROL_2

1Ex001B 0x1043 DATA_SWITCH_STATUS

1Ex001C 0x0000 LS_CH_CONTROL_1

1Ex001D 0x0000 HS_CH_CONTROL_1

1Ex001E 0x0000 EXT_ADDRESS_CONTROL

1Ex001F 0x0000 EXT_ADDRESS_DATA

1Ex8003 0x0283 VS_10G_LN_ALIGN_ACODE_P

1Ex8004 0x017c VS_10G_LN_ALIGN_ACODE_N

1Ex8021 0x000f MC_AUTO_CONTROL

1Ex802A 0x02fd DST_ON_CHAR_CONTROL

1Ex802B 0x02fd DST_OFF_CHAR_CONTROL

1Ex802C 0x0207 DST_STUFF_CHAR_CONTROL

1Ex802D 0x02fd DSR_ON_CHAR_CONTROL

1Ex802E 0x02fd DSR_OFF_CHAR_CONTROL

1Ex802F 0x0207 DSR_STUFF_CHAR_CONTROL

1Ex8040 0x0000 LATENCY_MEASURE_CONTROL

1Ex8041 0x0000 LATENCY_COUNTER_2

1Ex8042 0x0000 LATENCY_COUNTER_1

1Ex8100 0x0000 TRIGGER_LOAD_CONTROL

1Ex8101 0x0000 TRIGGER_EN_CONTROL

A register dump of the 0x1E device (VENDOR SPECIFIC) in the XAUI bridge configuration looks like this (NWP side):

reg value description

1Ex0000 0x0610 GLOBAL_CONTROL_1

1Ex0001 0x0b24 CHANNEL_CONTROL_1

1Ex0002 0x831d HS_SERDES_CONTROL_1

1Ex0003 0xa848 HS_SERDES_CONTROL_2

1Ex0004 0x1500 HS_SERDES_CONTROL_3

1Ex0005 0x2000 HS_SERDES_CONTROL_4

1Ex0006 0xf115 LS_SERDES_CONTROL_1

1Ex0007 0x0000 LS_SERDES_CONTROL_2

1Ex0008 0x0000 LS_SERDES_CONTROL_3

1Ex0009 0x0380 HS_OVERLAY_CONTROL

1Ex000A 0x1fff LS_OVERLAY_CONTROL

1Ex000B 0x0d10 LOOPBACK_TP_CONTROL

1Ex000C 0x0371 LS_CONFIG_CONTROL

1Ex000D 0x2f80 CLK_CONTROL

1Ex000E 0x0000 RESET_CONTROL

1Ex000F 0x70af CHANNEL_STATUS_1

1Ex0010 0x0000 HS_ERROR_COUNTER

1Ex0011 0x0000 LS_LN0_ERROR_COUNTER

1Ex0012 0x0000 LS_LN1_ERROR_COUNTER

1Ex0013 0x0000 LS_LN2_ERROR_COUNTER

1Ex0014 0x0000 LS_LN3_ERROR_COUNTER

1Ex0015 0x4142 LS_STATUS_1 (lane0)

1Ex0015 0x4142 LS_STATUS_1 (lane1)

1Ex0015 0x4142 LS_STATUS_1 (lane2)

1Ex0015 0x4142 LS_STATUS_1 (lane3)

1Ex0016 0xf006 HS_STATUS_1

1Ex0017 0x2000 DST_CONTROL_1

1Ex0018 0x0c20 DST_CONTROL_2

1Ex0019 0x2500 DSR_CONTROL_1

1Ex001A 0xac20 DSR_CONTROL_2

1Ex001B 0x1043 DATA_SWITCH_STATUS

1Ex001C 0x0000 LS_CH_CONTROL_1

1Ex001D 0x0000 HS_CH_CONTROL_1

1Ex001E 0x0000 EXT_ADDRESS_CONTROL

1Ex001F 0x0000 EXT_ADDRESS_DATA

1Ex8003 0x0283 VS_10G_LN_ALIGN_ACODE_P

1Ex8004 0x017c VS_10G_LN_ALIGN_ACODE_N

1Ex8021 0x000f MC_AUTO_CONTROL

1Ex802A 0x02fd DST_ON_CHAR_CONTROL

1Ex802B 0x02fd DST_OFF_CHAR_CONTROL

1Ex802C 0x0207 DST_STUFF_CHAR_CONTROL

1Ex802D 0x02fd DSR_ON_CHAR_CONTROL

1Ex802E 0x02fd DSR_OFF_CHAR_CONTROL

1Ex802F 0x0207 DSR_STUFF_CHAR_CONTROL

1Ex8040 0x0000 LATENCY_MEASURE_CONTROL

1Ex8041 0x0000 LATENCY_COUNTER_2

1Ex8042 0x0000 LATENCY_COUNTER_1

1Ex8100 0x0000 TRIGGER_LOAD_CONTROL

1Ex8101 0x0000 TRIGGER_EN_CONTROL

Any recommendations to debug this issue would be highly appreciated.

Thank you very much in advance for feedback & support!

BR

Joerg