Tool/software:

Hi, TI expert

The EMI test of the board with DP83826 applied by the customer has failed.

Regarding the EMI test, we would like to inquire about the cause and possible solution.

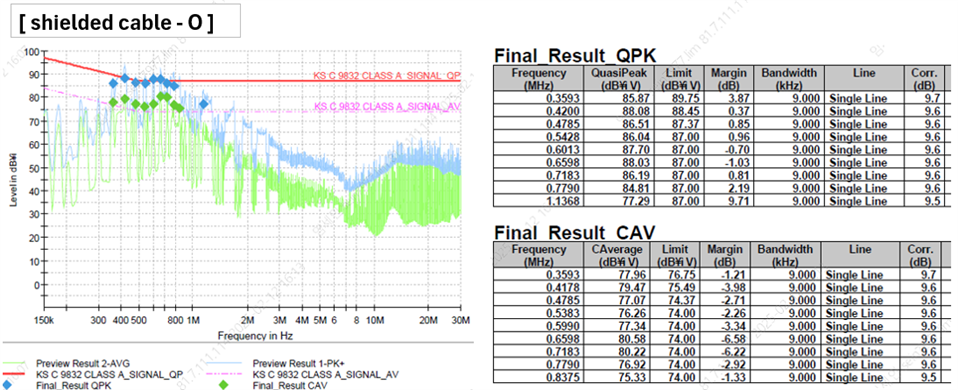

The customer confirmed that there was a problem where the specifications were exceeded in the 400KHz~1MHz band.

They tried using shielded cables instead of traditional UTP cables, and while there was some improvement, there was no significant change.

I am attaching the circuit diagram and PCB drawing for your reference.

Q1) Have you had a similar case? Are there any possible causes and solutions to EMI problems? Is there anything I can refer to to solve EMI?

Please check. Thank you.