Hi,

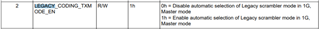

Could you please tell me regarding the legacy scrambler mode in 1G PCS master mode below?

a. Differences between legacy scrambler mode and normal scrambler mode

b. Legacy scrambler mode scrambling method details

c. Trigger that selects legacy scrambler mode

d. Conditions that legacy scrambler mode is detected incorrectly

e. How to prevent detection of legacy scrambler mode (How to work in normal scramble mode only)

f. Competitive part numbers that operate in legacy scrambler mode if you know

g. Is legacy scrambler mode TI intellectual property?

Best regards,

Kato