Tool/software:

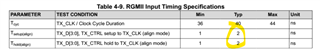

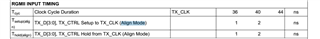

I plan to set internal delay for 100base T1 RGMII and TX and RX delay shall be set at PHY side.

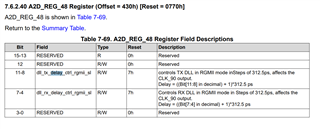

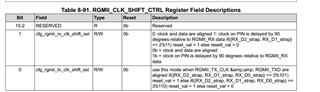

- If align mode is used during strap setting, and cfg_rgmii_rx_clk_shift_sel=1b cfg_rgmii_tx_clk_shift_sel=1b

what is the RGMII internal delay of TX and RX? only 2 ns? datasheet shows only 2ns.

- If RGMII (TX and RX Internal Delay Mode) is used during strap setting,

What is the RGMII internal delay of TX and RX? 5 ns? because default setting of below register setting:

dll_tx_delay_ctrl_rgmii_sl: 0xFh(5ns);

dll_rx_delay_ctrl_rgmii_sl: 0xFh(5ns);

- cfg_rgmii_rx_clk_shift_sel cfg_rgmii_tx_clk_shift_sel describe if set to 1b then there is 90 degree between clk and data.

- if RGMII align mode used, then the TX and RXD internal delay is 10ns?

- if RGMII (TX and RX Internal Delay Mode) is used, then the TX and RXD internal delay is 15ns?