Other Parts Discussed in Thread: DP83826E, DP83826EVM, HSEC180ADAPEVM

Tool/software:

Hello,

I am looking for guidance on CEXT capacitor on the DP83826I and DP83826E.

This old thread came as an authoritative answers:

https://e2e.ti.com/support/interface-group/interface/f/interface-forum/935079/dp83826i-dp83826-cap-on-cext-pin

However, here are the contradictions:

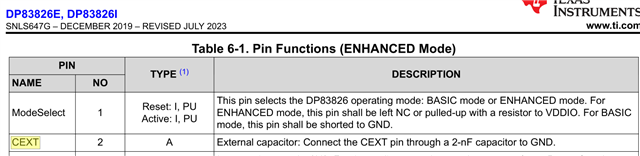

1- Datasheet States: External capacitor: Connect the CEXT pin through a 2-nF capacitor to GND.

Note this is the only mention of CEXT in the whole datasheet.

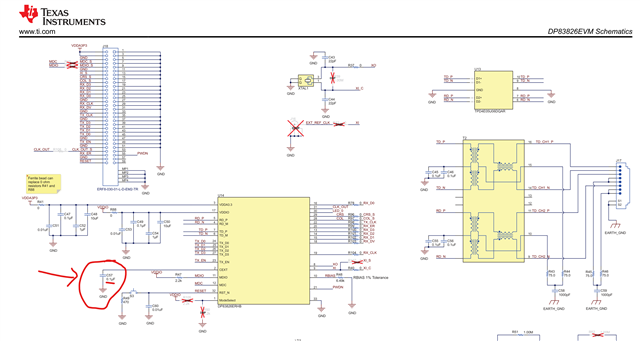

2- DP83826EVM uses a 0.1uF capacitor instead of 2nF.

From SNLU262A – DECEMBER 2019 – REVISED JUNE 2023. Figure 6-2 and Table 7-1.

www.ti.com/.../SNLU262

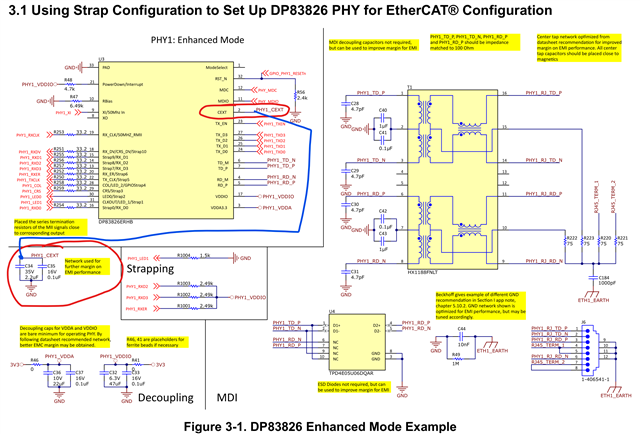

3- EtherCAT app note uses 2.2uF+0.1uF instead of 2nF.

Application Note: How and Why to Use the DP83826 for EtherCAT Applications

SNLA344C – MARCH 2022 – REVISED OCTOBER 2023

https://www.ti.com/lit/pdf/SNLA344

Figure 3-1

Note this is the only time an explanation is given: Network used for further margin on EMI performance

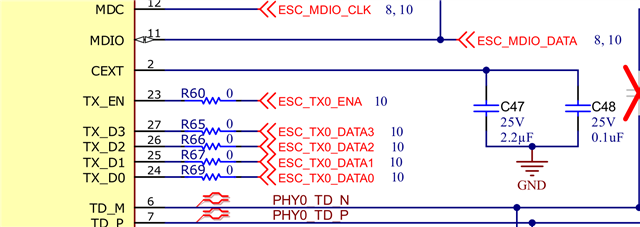

4- HSEC180ADAPEVM uses 2.2uF+0.1uF

This board docks the C2000 we are evaluation, and includes 2x DP83826E for EtherCAT communication.

From HSEC180ADAPEVM Design Files Package

https://www.ti.com/lit/zip/spac002

MCU134A_SCH.pdf

Sheet 7 of 13 and 8 of 13.

=====

The questions are:

1- Is the 2nF recommendation still valid?

5 year old referrenced questions stated putting 1uF on the EVM was an error and will be corrected. I now see TI doubled-down on extra capacitance.

A range instead of a value would help a lot.

2- What is CEXT for, exactly?

Knowing the function would help designers make adequate adaptations

3- Is there real EMC concerns for this pin?

As suggested by the EtherCAT app note. Knowing the expected frequencies would be required to properly build a capacitive network.

If designers are using their own judgement to deviate from datasheet, without adverse effects, then it should not be such a big deal. However, seeing ALL the TI physical realisations so far away from the recommendation puzzles me, a lot.

JosefMieslinger & Hermann Weigl: Did your design work out good with 2nF? Any notable troubles in EMC?

Justin Lazaruk: Did the situation change since your last answer?

Thanks!