Tool/software:

I have a question about the reset timing requirements for the TCA6424A.

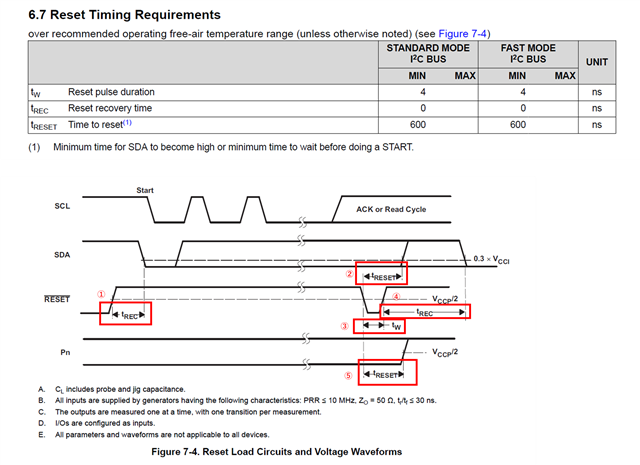

The relevant parts of the datasheet are "6.7 Reset Timing Requirements" and "Figure 7-4. Reset Load Circuits and Voltage Waveforms".

Could you please elaborate on when the reset requirement needs to be respected?

(Could you please explain in detail about the timing of each of the items in the red boxes below (① to ⑤)?)

Best regards