- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

Tool/software:

I have a question about the reset timing requirements for the TCA6424A.

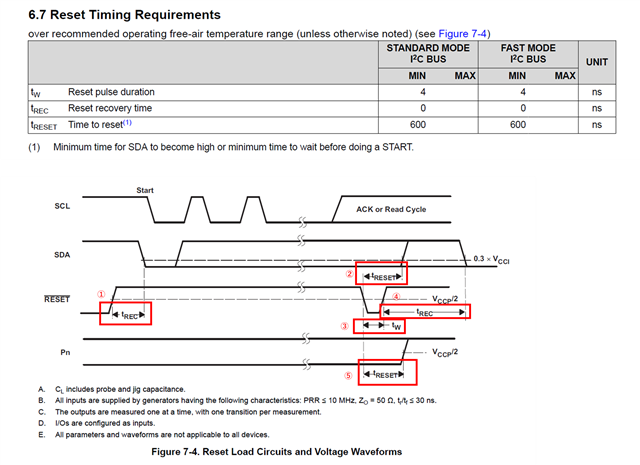

The relevant parts of the datasheet are "6.7 Reset Timing Requirements" and "Figure 7-4. Reset Load Circuits and Voltage Waveforms".

Could you please elaborate on when the reset requirement needs to be respected?

(Could you please explain in detail about the timing of each of the items in the red boxes below (① to ⑤)?)

Best regards

Hi User6448843,

tW = RESET pulse duration. This is the time needed to hold /RESET below a VCCP/2 voltage for a valid /RESET pulse. The width of the pulse needs to be at least 4 ns in length for it to be considered a valid /RESET pulse. Anything faster than this, and the reset condition may not be recognized by the I/O expander.

tREC = RESET recovery time. After a successful reset condition is given (high-low-high on /RESET pin), there exists some time before an I2C start condition can be issued. In this case, the tREC = 0 ns, so after a reset condition, a start condition can immediately occur.

tRESET = Time to RESET. In the graph, the example is if SDA is held LOW or an I/O (Pn) is held LOW/HIGH, at what time will the I/O expander reset back to its default state. On the falling edge of /RESET being toggled, you need at least 600 ns of time to see Pn or SDA go back to their initial conditions.

Please let me know if you have any additional questions.

Regards,

Tyler

Please tell me about the tREC regulations in 6.7 (Reset Timing Requirements).

The MIN (0 ns) is specified, but the MAX time is not.

Does this mean that the bus can be used immediately after reset?

Best regards.

Hi User6448843,

Does this mean that the bus can be used immediately after reset?

You are correct.

Technically speaking, as soon as /RESET passes the 0.7 x VCCI = VIH threshold, the /RESET condition is released, and the bus can be used normally according to the tREC spec.

Regards,

Tyler