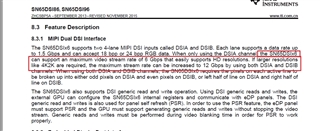

Part Number: SN65DSI86

Tool/software:

Hello:

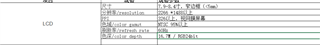

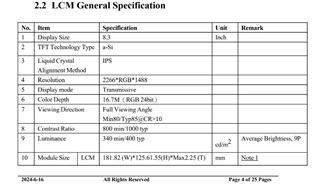

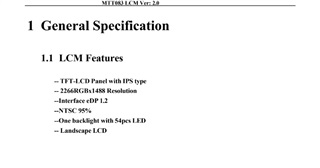

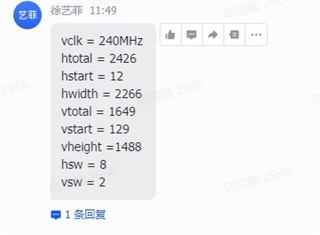

The customer's screen display requirements are as follows. May I ask if it is necessary to connect two DSIs to complete the requirements? Is it possible for the customer to only connect one DSI route? Thank you