Part Number: SN65MLVD206B

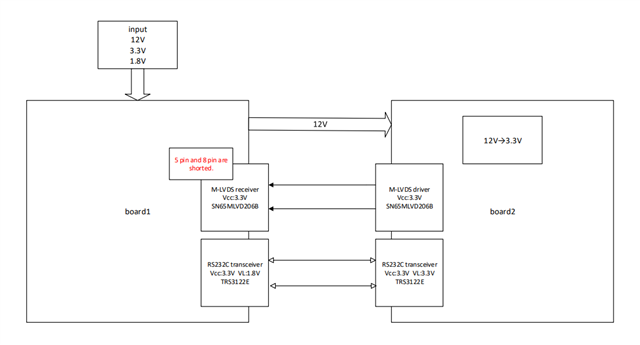

Other Parts Discussed in Thread: TRS3122E, STRIKE

Tool/software:

Hello,

We are designing the SN65MLVD206B in receiver mode, and if there is some input on A and B (pins 6 and 7) while the power is off, is there a possibility of failure due to overcurrent or other reasons?

In our analysis, it seems that pins 5 and 8 of the SN65MLVD206B are shorted.

We think the cause is due to a mistake in the order of power input.