Part Number: DS280DF810

Tool/software:

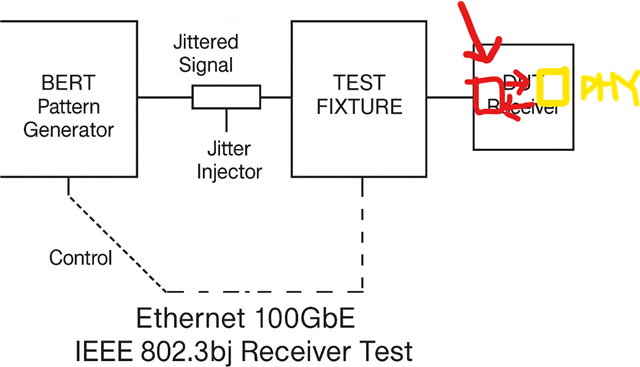

Hi team expert,

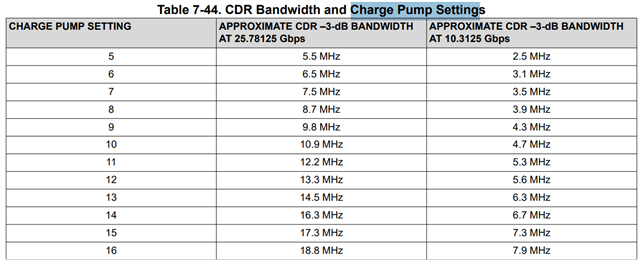

Regarding the IEEE802.3bj receiver test, I know increase our CDR bandwidth can track faster jitter when necessary but also brings a little residual jitter to the post-stage of the signal path,

May I say lowest CDR bandwidth might be the optimal setting "under the premise" that our retime sampler can track all patterns with the high-frequency Sj that is injected,

so the attenuated residual jitter impact would be smallest to the whole system test?