Part Number: DP83869HM

Other Parts Discussed in Thread: DP83869

Tool/software:

Hi,

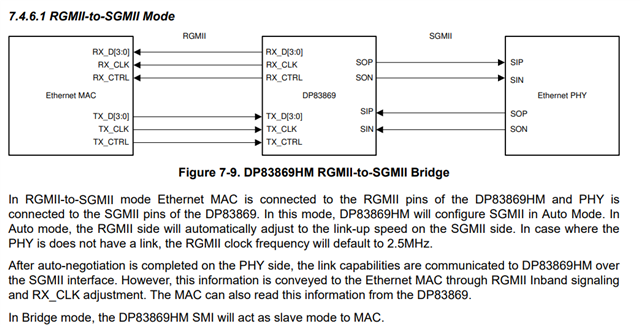

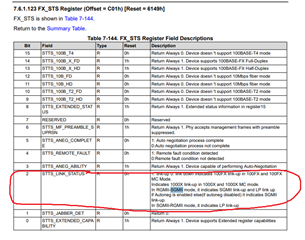

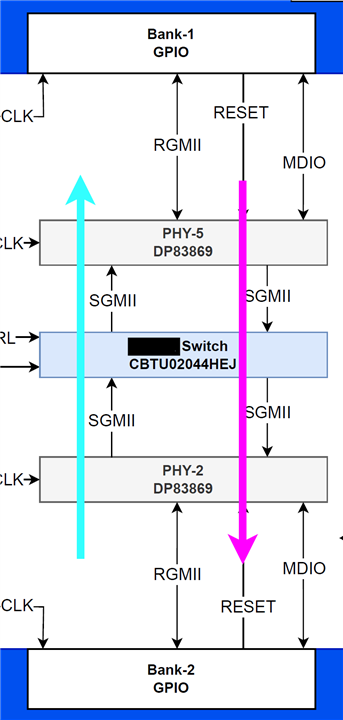

I am currently troubleshooting a design where we are trying to establish unidirectional communication between two FPGAs using PHYs in a SGMII back-to-back configuration. The unidirectional communication is enforced by disconnecting the RX SGMII diff pairs corresponding to the FPGA that is transmitting data.

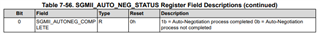

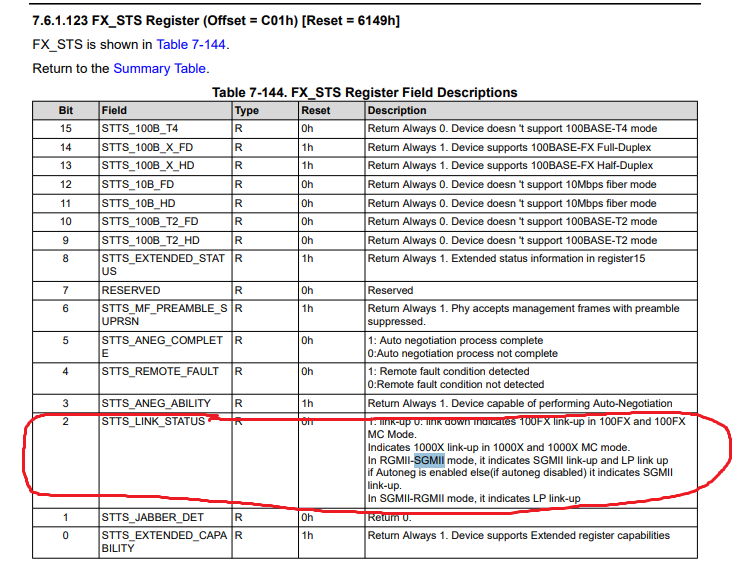

We have probed the TX clock signals for the FPGAs using an oscilloscope and the measured frequency is 125 MHz. This is correct because the MAC interfaces have a configured link speed of 1000 Mbps. The RX clock signals for the PHYs have a frequency of 2.5 MHz, which I'm assuming means no link has been established or there is some other issue going on.

See my list of questions below.

1. Is this SGMII back-to-back configuration feasible?

2. Can the PHYs work with only 2 out of the 4 signals being connected between them?

3. Are there any special register configurations that are required to get this working? I read in an old forum post that mentioned auto negotiation needs to be disabled.

4. What are the steps to getting MII loopback mode working? I've been unable to this mode working.

Thanks,

Jean