Part Number: SN65DSI83

Other Parts Discussed in Thread: DSI-TUNER

Tool/software:

We are creating our own printed circuit board, outputting MIPI from a device called i.MX8, and attempting to perform LVDS conversion for an LCD monitor.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Part Number: SN65DSI83

Other Parts Discussed in Thread: DSI-TUNER

Tool/software:

We are creating our own printed circuit board, outputting MIPI from a device called i.MX8, and attempting to perform LVDS conversion for an LCD monitor.

However, despite configuring the settings within the device, no video is being output to the LCD monitor, and we get 0x80 error when read 0xE5.

Could you please provide support for this matter?

The following checks have been completed, and we recognize that there are no issues: 1) Timing in Table 7-2 of the datasheet 2) Display of the color bar when register 0x3C is set

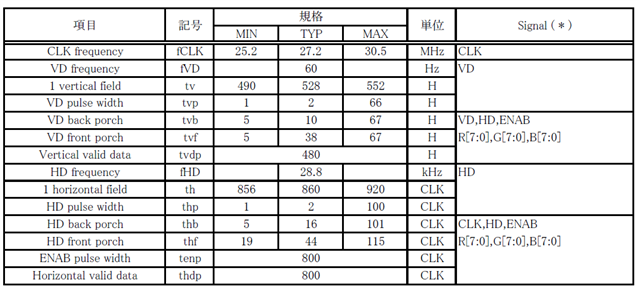

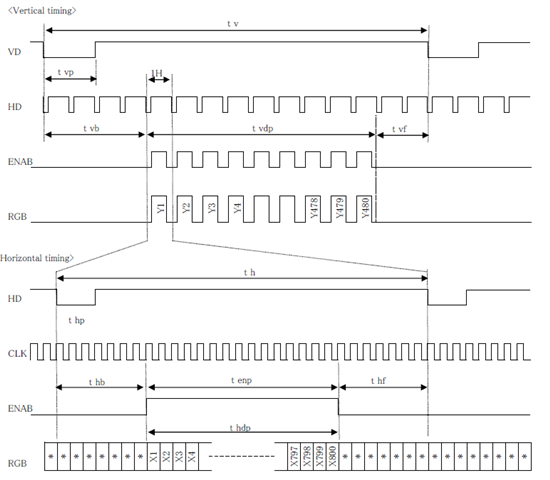

our LCD monitor display spec

our I2c settimg

I2C_setting.csv

Hi Yoshifumi,

A few follow-up questions:

Since reg 0xE5 is showing 0x80 VS/HS sync error - please start by checking the VS/HS sync polarity of your LCD monitor(not shown in table) and ensure it matches with the register setting in 0x18.

Thanks,

Ragav Subramanian

Hi Ragav-san

・No, I didn’t use DSI-tuner.

I saw that this file was mentioned in E2E, but I couldn't install it.

SN65DSI83ZXHR: unable to reset the LVDS bridge through software and no output on display - Simulation, hardware & system design tools forum - Simulation, hardware & system design tools - TI E2E support forums

・MIPI DSI settings from i.MX8

CLK 163MHz

lane count 2

resolution 800 x 480

horizontal 800 + 44 + 2 + 14

vertical 480 + 38 + 2 + 8

・The VS/HS sync polarity of LCD

I changed it and I can display LCD.

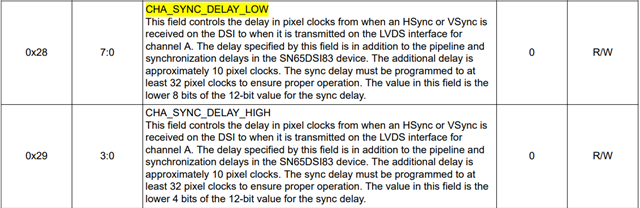

CHA_SYNC_DELAY_LOW 0x00 -> 0x21

Please tell me what values this setting should have and how I should evaluate them.

Hi Yoshifumi,

Glad to hear the system is operating now.

The CHA_SYNC_DELAY_LOW 0x00 -> 0x21 is the additional delay in the device for outputting H/Vsync High to Low transition. The CHA_SYNC_DELAY_LOW and CHA_SYNC_DELAY_HIGH registers must be greater than 32 per the datasheet. The 0x21 passes this requirement and allows the appropriate delay for the output - please ensure CHA_SYNC_DELAY_HIGH is also within the requirement

Thanks,

Ragav Subramanian

Hi Ragav-san

Thank you for your answer. Regarding the register setting value, Currently it's working fine with 0x21, but could you please advise on how to fine-tune it, such as using 0x22 or 0x23...etc, and what specific adjustments should be made?

Hi Yoshifumi-san,

The minimum requirement for the register is 0x20 (32 pixel clocks delay).

I would advise the following criteria to use as a rough guideline to find appropriate delay values:

Once a working value is found, I would not expect much variation in value needed; however, the customer can run some longer stress tests and POR testing to ensure the setting is robust.

Thanks,

Ragav Subramanian