Other Parts Discussed in Thread: DP83825EVM

Tool/software:

Hello TI team,

This is a follow-up to my earlier question regarding the DP83825I REF_CLK during power ramp-up: https://e2e.ti.com/support/interface-group/interface/f/interface-forum/1486923/dp83825i-clock-availability-at-power-ramp/5715771#5715771

We have updated our design based on your recommendation and now assert RESET after REF_CLK is stable. However, after this change, we noticed the following behavior:

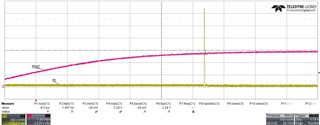

- We observe a single spike/glitch on the RX_ER/DV pin after RESET is deasserted (see attached oscilloscope screenshot).

- RX_ER/DV is used as a bootstrap pin, with a 2.49 kΩ pulldown as recommended in the datasheet.

- After the glitch, RX_ER remains low, and the PHY seems to boot correctly.

- RESET and REF_CLK ramp-up seem correct, and the spike appears only once.

glitch appears just after RESET rises.

My questions:

- Is this a known problem with RX_ER showing a glitch after RESET deassertion?

- Can this glitch affect the bootstrap sampling, or is it safe as long as RX_ER is low at the moment RESET rises?

Thanks in advance for your support!

Best regards,

Hamza