Tool/software:

Good day,

I have question regarding the DP83TC812R-Q1 strapping.

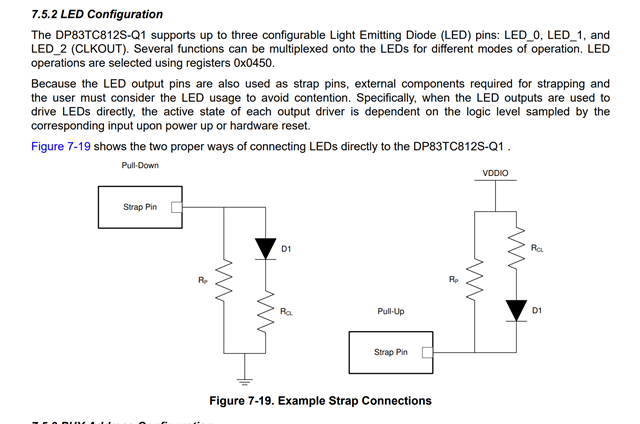

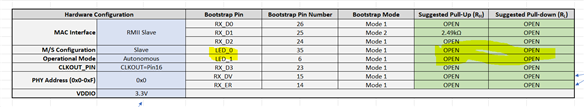

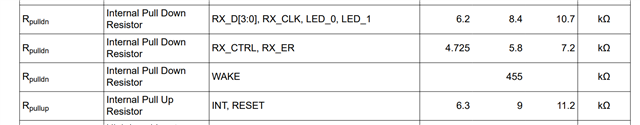

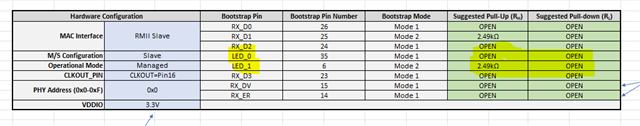

The strap configuration i'm looking for using TI tool requires pins LED1/0 to be OPEN during power up.

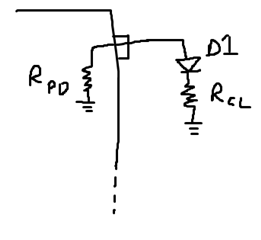

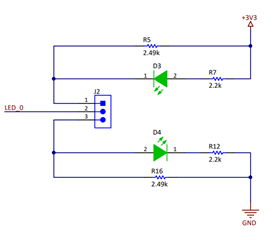

However if LEDs are attached with their own resistors OPEN can't be achieved since LED will either pull it up or down with some voltage delta.

Could you confirm what OPEN state mean and if LED can be attached to those pins if OPEN is needed for strap?

Thank you.