Other Parts Discussed in Thread: LMK3H0102

Tool/software:

Joynext has report 2 new flash- screen case of 941AS which they have reported before. 1 pcs from After-sales Field and the other from VW assembly plants. The 2 pcs of flash- screen Head-units returned to JNN in last June.

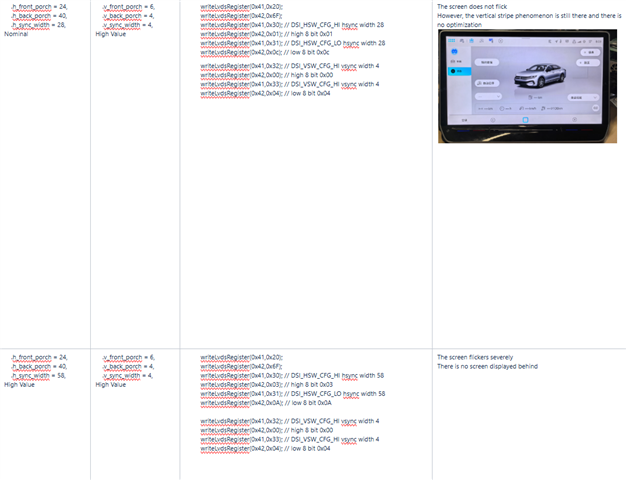

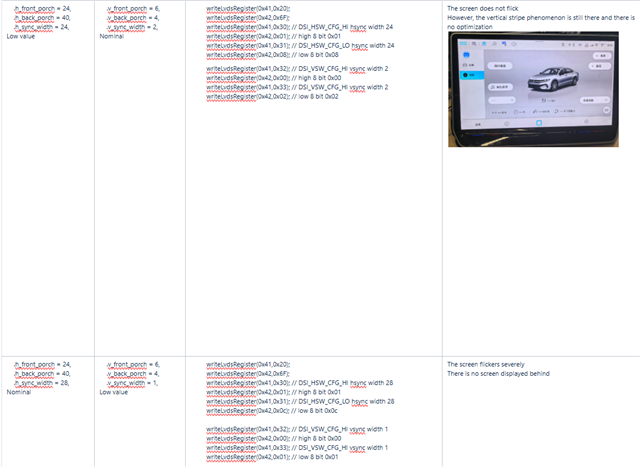

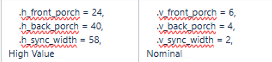

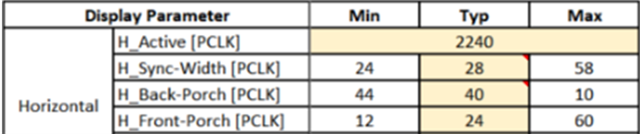

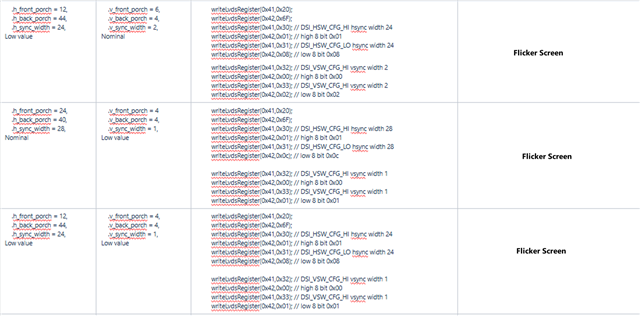

On the condition of flash- screen phenomena reproducing, they tried the actions below:

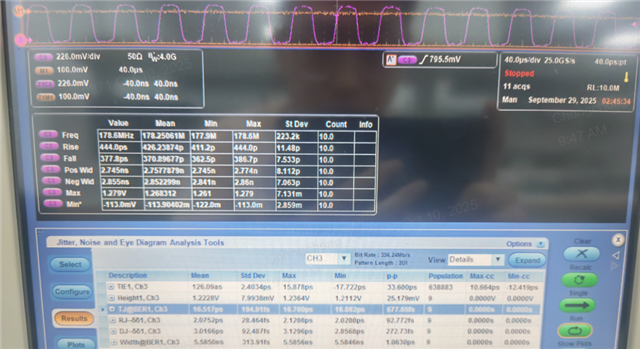

- 3rd party company measures and records the pictures and signals of each frame that SOC outputs with the tool signal analyzer, report as attached: 01-d0.pdf

- There is no DSI error on the device of signal analyzer and no flash-screen issue when playing back the pictures recorded by signal analyzer ;

So they concluded that there is no errors with the SOC outputting signals.

Base on above, they insist on the failure was caused by 941, and request TI to continue to assist in the next step analysis:

Measure the following four types of PCBAs with signal analyzer to check whether the DSI error occurs;

- 1 piece of OK PCBA that does not flash screen , 1 piece of flashing screen PCBA, 2 piece of PCBA ---done the test of AB between two PCBAs ;

- Testing Environment construction: 1pcs of wiring harness, test screen, CAN line(it could be removed )

Can you please help support on this case to help them find the root cause of the flash- screen? And provide express receiver and address information to get the new returned ECU with 941

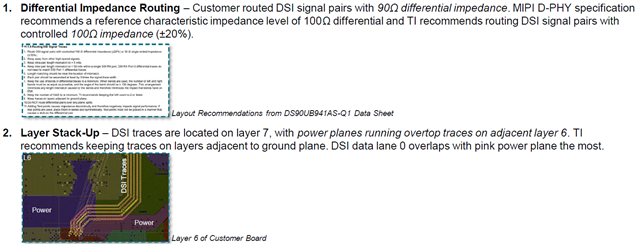

BU analysis results before:

Joyson DS90UB941AS-Q1 flashing screen issue accelerate Dec 16.pdf

Joyson - DS90UB941AS-Q1 Flickering Screen Analysis and Root Cause Theory.pdf

Best Regards,

Xiaowei Zhang