Tool/software:

Hello,

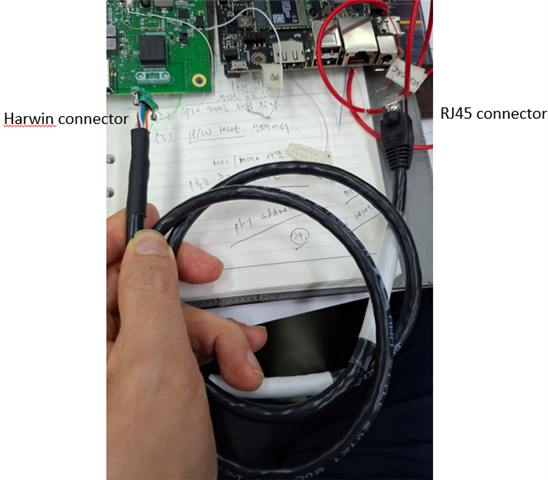

My customer wants to use DP83867IS in conjunction with NVIDIA Jetson AGX Orin's SOM.

They have an issue with the RGMII interface not working between the DP83867IS and the NVIDIA SOC.

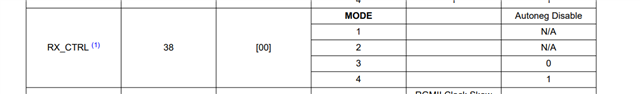

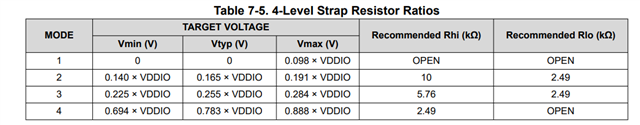

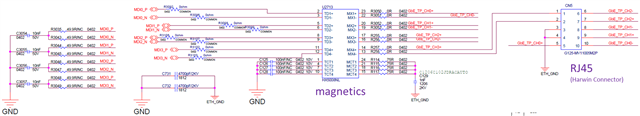

Q1. Please review the circuit design below to see if there are any problems.

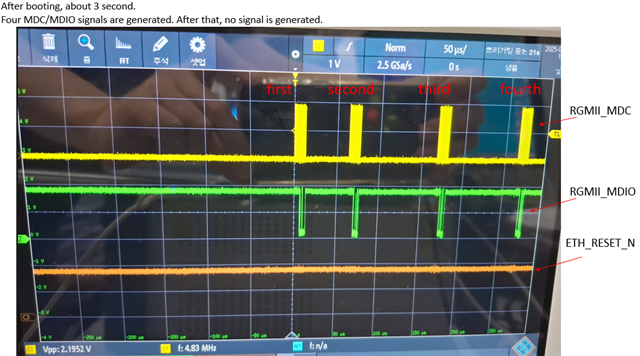

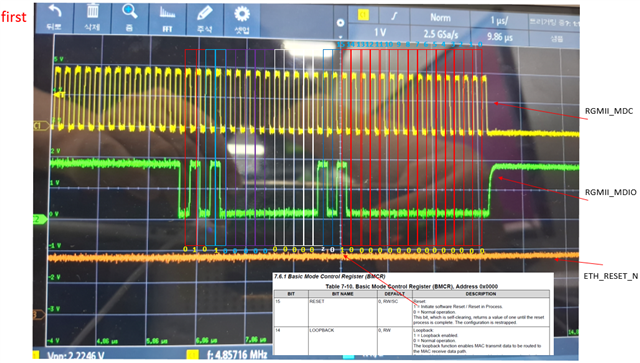

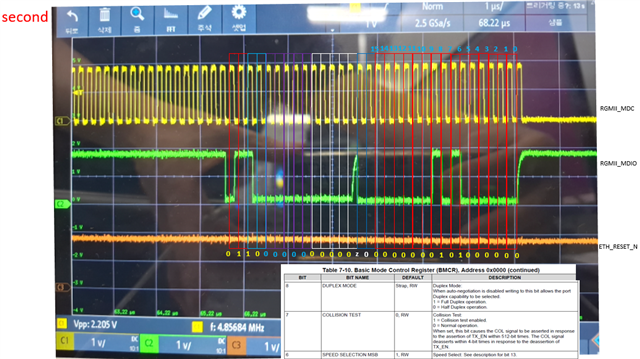

Q2. The files below are images capturing the power sequence and clock signal of the DP83867IS.

Q2-1. Referring to the second image on page 1, the output of the XI signal is output about 85mS after the 1.0V power supply is stabilized. It seems that the clock output is too late. Could this cause a problem in the operation of the DP83867IS? (Please refer to the clock signal output on page 2)

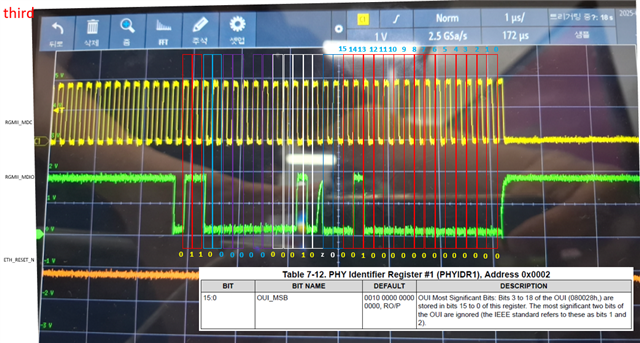

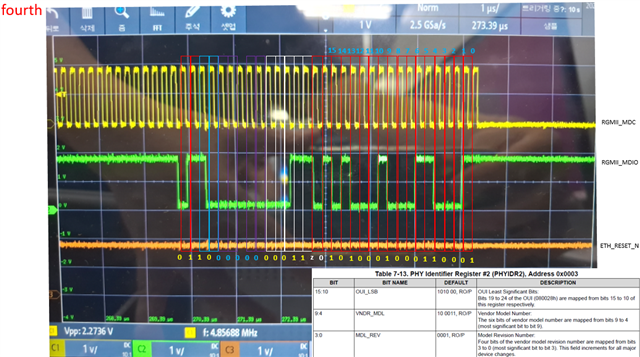

Q2-2. Referring to the first image on page 3, they thought that the clock signal was output late because of the NVIDIA Reset signal, so they changed the reset signal to H/W reset. Are the resets they changed correct?

DP83867 power sequency and Clock output.pdf

Q3. Has DP83867IS been used with NVIDIA SOCs before? Please advise on this use case

Thank you.

JH