Tool/software:

Hello,

I would like to ask a general question about Ethernet PHY use case.

Generally, desktop computers are turned off without unplugging the LAN cable. (Link partner : Router/Switching HUB is powered up, but, the computer itself using the PHY is power off.)

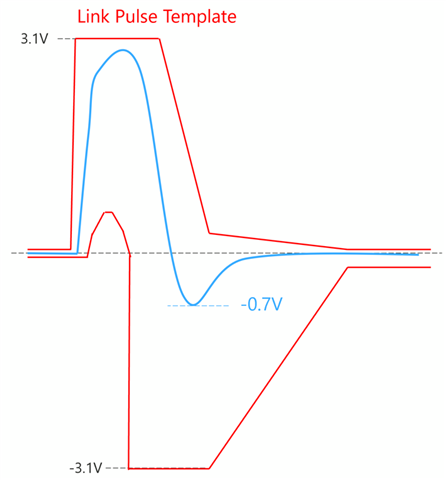

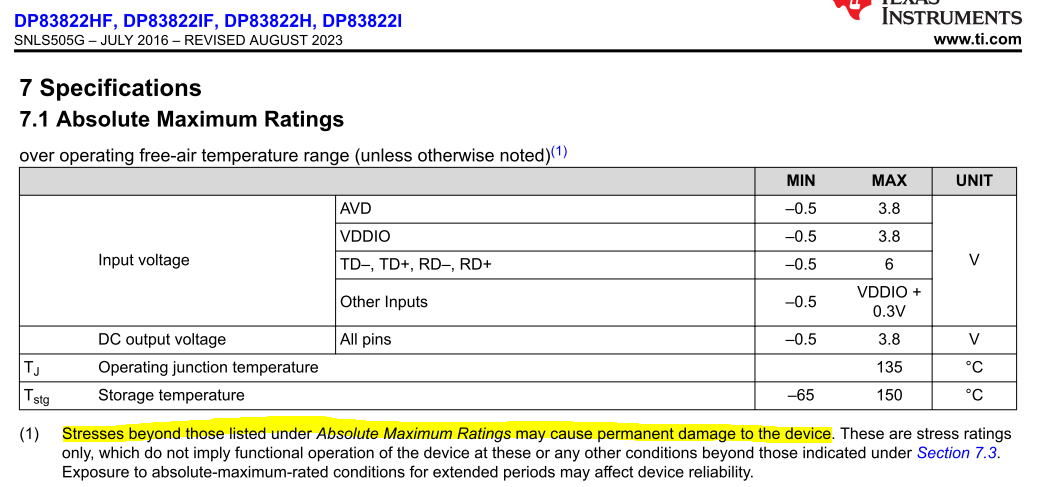

In this situation, Ethernet PHY in this computer continuously receive NLP/FLP which could have undershoot below the Absolute Maximum Rating described in the datasheet.

Undershoot may depend on board design, however, I can find some waveform which is exceeding -0.5V in E2E.

Since the device is receiving the voltage which exceeds the Absolute Maximum Rating, I am thinking that the device could be damaged.

<Question1>

Is TI device designed to withstand such use case ?

Most of the device seems to have Absolute Maximum Rating MIN as -0.3V or -0.5V for MDI pins.

<Question2>

Is it not recommended to connect the LAN cable before the system (PHY) power up ?

Best Regards,

Kawai