Tool/software:

Hello ePHY team,

- Can you please provide more detail on the purpose of the XI input clock?

- In the datasheet, the term "local reference clock" is used. Does that refer to the XI input clock? If so, then it's conflicting with the text I highlighted below. The text says the local reference clock is recovered

from the Ethernet packet.

- My confusion is this:

- If we recover the clock from the network for RX_CLK and if we receive the clock from the MAC for GTX_CLK, then why do we need the XI clock?

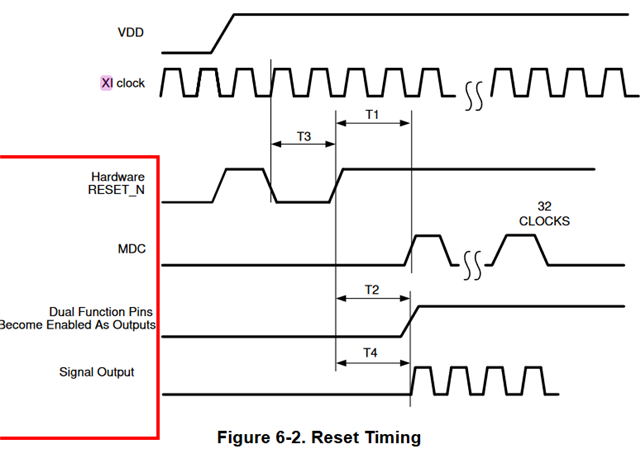

- I don't see other timing diagrams using the XI besides the start-up or reset, I guess it's used for the MDC? Also, what is "Signal Output" mean in Figure 6-2?

Thank you,

Jennifer