Part Number: SN65DSI86

Tool/software:

Hello:

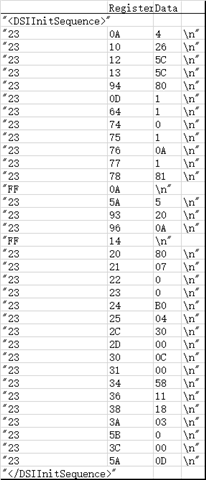

My customer uses SN65DSI86 for his project,

Problem description: High probability of occurrence, the power key cannot light up the screen

Phenomenon: Press the power button to turn on the screen, and the backlight will light up before the display. There is a low probability of the problem where only the backlight will light up and not display

Device information

Screen: N402-CM2001-000 T603AB/14 inch FHD/INX/HX8052-A01/Panda/KD/National Display

Transfer IC: SN65DSI86

Screen FAE confirmation: If the 3.3V power supply of the screen is normal, the screen can work normally. The screen power supply is provided by LDO, and the actual measurement shows that the screen power supply is normal

Current question:

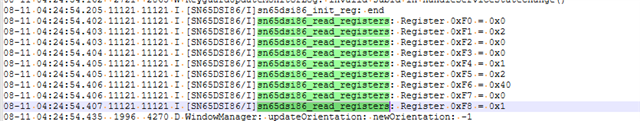

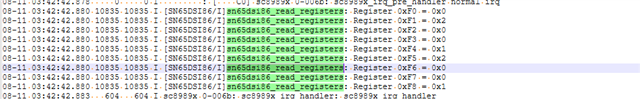

according to SN65DSI86: LOSS_OF_DP_SYNC_LOCK_ERR - Interface forum - Interface - TI E2E support forums The debug method in the post introduces VSYNC and HSYNC. The measured frequency of HSYNC is 73.6kHz, and there is no change in frequency between normal display and abnormal non display.

SN65DSI86: LOSS_OF_DP_SYNC_LOCK_ERR - Interface forum - Interface - TI E2E support forums

Please help confirm the following questions:

1、How to determine the problem point after measuring the HSYNC frequency?

2、What other configurations need to be checked for problem point confirmation when 0xF6=0x40?