Other Parts Discussed in Thread: SN75LVPE5421, DS320PR410, SN74LVC1G04

Tool/software:

Hi Team,

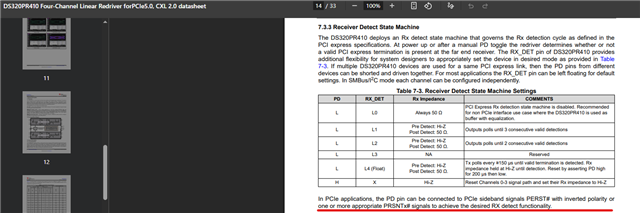

We use SN75LVPE5412&SN75LVPE5421 to design a Gen5 PCIe X4 AIC for MCIO 38P.

Unlike DS320PR410, there is no similar description in SN75LVPE5412 datasheet. What's the recommended connection of PD pin if we use SN75LVPE5412&SN75LVPE5421? Thank you.