Other Parts Discussed in Thread: SN65LVDS31

Tool/software:

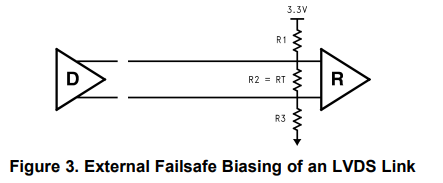

Hi, I am using the SN65LVDS32 for a design for handling CAT5 data signals. With my current schematic the pins are left in an unpredictable state when no signal is being sent into the CAT5 input jack.

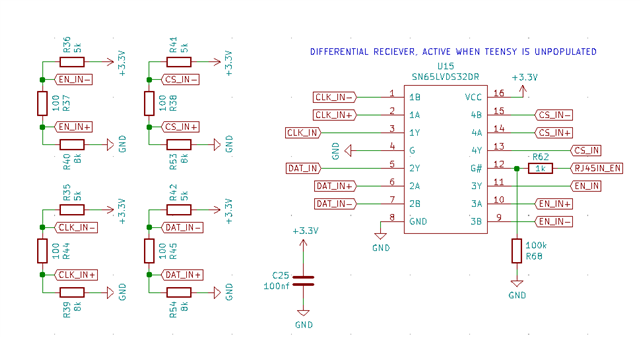

This is my current schematic, with a 100 ohm hysteresis resistor across the differential inputs and both + and - signals biased to ground by 10k resistors:

I find with CAT5 signal coming in from an SN65LVDS31 this schematic works for me.

But when nothing is plugged in some of the outputs are high and some are low, seemingly at random.

When no differential signal is being received I need all the outputs to go low. What do I need to change to accomplish this?

Please advise.