Part Number: DP83825I

Other Parts Discussed in Thread: AM4378

Tool/software:

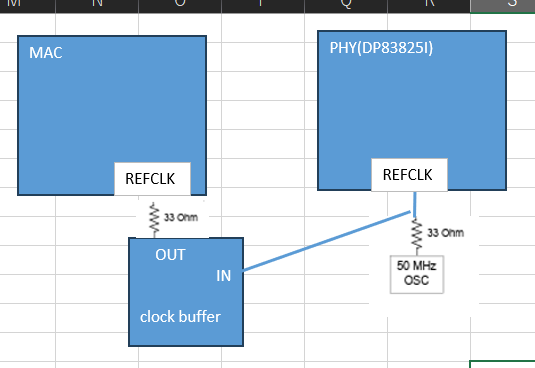

In slave mode, a 50MHz CMOS-level oscillator is connected to the XI pin and also to the MAC's refclk pin.

Are there any layout specifications for this CLK line? I'm curious about the following:

- Should the oscillator be placed closer to the MAC or the PHY?

- Are there any restrictions on the distance between the PHY and MAC?