Part Number: SN65DSI86

Tool/software:

Hello:

There is a problem when customer uses sn65dsi86

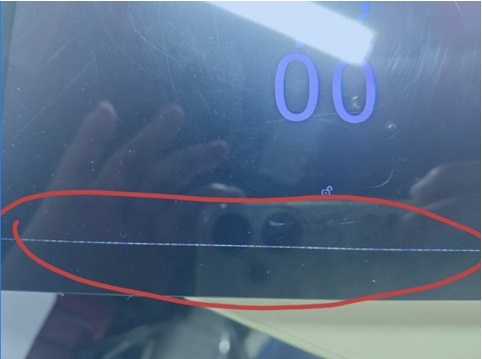

Problem phenomenon: There is a probability of flashing color bars at the bottom when the screen is lit up

1. After powering on and initializing the sn65dsi86, the screen will light up with a probability of flashing color bars at the bottom; After the screen is turned off and the power is turned off, there is still a probability that this abnormal phenomenon will occur again when the sn65dsi86 is powered on again;

2. The port output by mipi is the required port parameter for the screen;

3 htotal :2426 vtotal:1649,60Hz ; Single port, 4-lane

How should abnormal phenomena be eliminated? What is the reason for the occurrence? Thanks!!!