Other Parts Discussed in Thread: DP83869, AM6442

Tool/software:

ethernetA = &cpsw_port1;

ethernetB = &icssg1_emac1;

ethernetC = &icssg1_emac0;

ethernetD = &icssg0_emac1;

ethernetE = &icssg0_emac0;

icssg0_eth: icssg0-eth {

status = "okay";

compatible = "ti,am642-icssg-prueth";

pinctrl-names = "default";

pinctrl-0 = <&icssg0_rgmii1_pins_default>, <&icssg0_rgmii2_pins_default>;

sram = <&oc_sram>;

ti,prus = <&pru0_0>, <&rtu0_0>, <&tx_pru0_0>, <&pru0_1>, <&rtu0_1>, <&tx_pru0_1>;

ti,iep = <&icssg0_iep0>, <&icssg0_iep1>;

firmware-name = "ti-pruss/am64x-sr2-pru0-prueth-fw.elf",

"ti-pruss/am64x-sr2-rtu0-prueth-fw.elf",

"ti-pruss/am64x-sr2-txpru0-prueth-fw.elf",

"ti-pruss/am64x-sr2-pru1-prueth-fw.elf",

"ti-pruss/am64x-sr2-rtu1-prueth-fw.elf",

"ti-pruss/am64x-sr2-txpru1-prueth-fw.elf";

ti,pruss-gp-mux-sel = <2>, /* MII mode */

<2>,

<2>,

<2>, /* MII mode */

<2>,

<2>;

ti,mii-g-rt = <&icssg0_mii_g_rt>;

ti,mii-rt = <&icssg0_mii_rt>;

ti,pa-stats = <&icssg0_pa_stats>;

interrupt-parent = <&icssg0_intc>;

interrupts = <24 0 2>, <25 1 3>;

interrupt-names = "tx_ts0", "tx_ts1";

dmas = <&main_pktdma 0xc100 15>, /* egress slice 0 */

<&main_pktdma 0xc101 15>, /* egress slice 0 */

<&main_pktdma 0xc102 15>, /* egress slice 0 */

<&main_pktdma 0xc103 15>, /* egress slice 0 */

<&main_pktdma 0xc104 15>, /* egress slice 1 */

<&main_pktdma 0xc105 15>, /* egress slice 1 */

<&main_pktdma 0xc106 15>, /* egress slice 1 */

<&main_pktdma 0xc107 15>, /* egress slice 1 */

<&main_pktdma 0x4100 15>, /* ingress slice 0 */

<&main_pktdma 0x4101 15>, /* ingress slice 1 */

<&main_pktdma 0x4102 0>, /* mgmnt rsp slice 0 */

<&main_pktdma 0x4103 0>; /* mgmnt rsp slice 1 */

dma-names = "tx0-0", "tx0-1", "tx0-2", "tx0-3",

"tx1-0", "tx1-1", "tx1-2", "tx1-3",

"rx0", "rx1",

"rxmgm0", "rxmgm1";

ethernet-ports {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

icssg0_emac0: port@0 { /* ETH-D */

status = "okay";

reg = <0>;

phy-handle = <&icssg0_phy2>;

phy-mode = "rgmii-id";

ti,syscon-rgmii-delay = <&main_conf 0x4100>;

/* Filled in by bootloader */

local-mac-address = [1C 63 49 1A DE 15];

};

icssg0_emac1: port@1 { /* ETH-E */

status = "okay";

reg = <1>;

phy-handle = <&icssg0_phy1>;

phy-mode = "rgmii-id";

ti,syscon-rgmii-delay = <&main_conf 0x4104>;

/* Filled in by bootloader */

local-mac-address = [1C 63 49 1A DE 16];

};

};

};

icssg1_eth: icssg1-eth {

status = "okay";

compatible = "ti,am642-icssg-prueth";

pinctrl-names = "default";

pinctrl-0 = <&icssg1_rgmii1_pins_default>, <&icssg1_rgmii2_pins_default>;

sram = <&oc_sram>;

ti,prus = <&pru1_0>, <&rtu1_0>, <&tx_pru1_0>, <&pru1_1>, <&rtu1_1>, <&tx_pru1_1>;

ti,iep = <&icssg1_iep0>, <&icssg1_iep1>;

firmware-name = "ti-pruss/am64x-sr2-pru0-prueth-fw.elf",

"ti-pruss/am64x-sr2-rtu0-prueth-fw.elf",

"ti-pruss/am64x-sr2-txpru0-prueth-fw.elf",

"ti-pruss/am64x-sr2-pru1-prueth-fw.elf",

"ti-pruss/am64x-sr2-rtu1-prueth-fw.elf",

"ti-pruss/am64x-sr2-txpru1-prueth-fw.elf";

ti,pruss-gp-mux-sel = <2>, /* MII mode */

<2>,

<2>,

<2>, /* MII mode */

<2>,

<2>;

ti,mii-g-rt = <&icssg1_mii_g_rt>;

ti,mii-rt = <&icssg1_mii_rt>;

ti,pa-stats = <&icssg1_pa_stats>;

interrupt-parent = <&icssg1_intc>;

interrupts = <24 0 2>, <25 1 3>;

interrupt-names = "tx_ts0", "tx_ts1";

dmas = <&main_pktdma 0xc200 15>, /* egress slice 0 */

<&main_pktdma 0xc201 15>, /* egress slice 0 */

<&main_pktdma 0xc202 15>, /* egress slice 0 */

<&main_pktdma 0xc203 15>, /* egress slice 0 */

<&main_pktdma 0xc204 15>, /* egress slice 1 */

<&main_pktdma 0xc205 15>, /* egress slice 1 */

<&main_pktdma 0xc206 15>, /* egress slice 1 */

<&main_pktdma 0xc207 15>, /* egress slice 1 */

<&main_pktdma 0x4200 15>, /* ingress slice 0 */

<&main_pktdma 0x4201 15>, /* ingress slice 1 */

<&main_pktdma 0x4202 0>, /* mgmnt rsp slice 0 */

<&main_pktdma 0x4203 0>; /* mgmnt rsp slice 1 */

dma-names = "tx0-0", "tx0-1", "tx0-2", "tx0-3",

"tx1-0", "tx1-1", "tx1-2", "tx1-3",

"rx0", "rx1",

"rxmgm0", "rxmgm1";

ethernet-ports {

#address-cells = <1>;

#size-cells = <0>;

status = "okay";

icssg1_emac0: port@0 { /* ETH-C */

status = "okay";

reg = <0>;

phy-handle = <&icssg1_phy1>;

phy-mode = "rgmii-id";

ti,syscon-rgmii-delay = <&main_conf 0x4108>;

/* Filled in by bootloader */

local-mac-address = [1C 63 49 1A DE 17];

};

icssg1_emac1: port@1 { /* ETH-B */

status = "okay";

reg = <1>;

phy-handle = <&icssg1_phy2>;

phy-mode = "rgmii-id";

ti,syscon-rgmii-delay = <&main_conf 0x410c>;

/* Filled in by bootloader */

local-mac-address = [1C 63 49 1A DE 18];

};

};

};

icssg1_mdio1_pins_default: icssg1-mdio1-default-pins {

pinctrl-single,pins = <

AM64X_IOPAD(0x015c, PIN_OUTPUT, 0) /* (Y6) PRG1_MDIO0_MDC */

AM64X_IOPAD(0x0158, PIN_INPUT, 0) /* (AA6) PRG1_MDIO0_MDIO */

>;

};

icssg0_mdio1_pins_default: icssg0-mdio1-default-pins {

pinctrl-single,pins = <

AM64X_IOPAD(0x0204, PIN_OUTPUT, 0) /* (P3) PRG0_MDIO0_MDC */

AM64X_IOPAD(0x0200, PIN_INPUT, 0) /* (P2) PRG0_MDIO0_MDIO */

>;

};

/* ETH-C RGMII pin muxing */

icssg1_rgmii1_pins_default: icssg1-rgmii1-default-pins{

pinctrl-single,pins = <

AM64X_IOPAD(0x00b8, PIN_INPUT, 2) /* (Y7) PRG1_PRU0_GPO0.PRG1_RGMII1_RD0 */

AM64X_IOPAD(0x00bc, PIN_INPUT, 2) /* (U8) PRG1_PRU0_GPO1.PRG1_RGMII1_RD1 */

AM64X_IOPAD(0x00c0, PIN_INPUT, 2) /* (W8) PRG1_PRU0_GPO2.PRG1_RGMII1_RD2 */

AM64X_IOPAD(0x00c4, PIN_INPUT, 2) /* (V8) PRG1_PRU0_GPO3.PRG1_RGMII1_RD3 */

AM64X_IOPAD(0x00d0, PIN_INPUT, 2) /* (AA7) PRG1_PRU0_GPO6.PRG1_RGMII1_RXC */

AM64X_IOPAD(0x00c8, PIN_INPUT, 2) /* (Y8) PRG1_PRU0_GPO4.PRG1_RGMII1_RX_CTL */

AM64X_IOPAD(0x00e4, PIN_OUTPUT, 2) /* (AA8) PRG1_PRU0_GPO11.PRG1_RGMII1_TD0 */

AM64X_IOPAD(0x00e8, PIN_OUTPUT, 2) /* (U9) PRG1_PRU0_GPO12.PRG1_RGMII1_TD1 */

AM64X_IOPAD(0x00ec, PIN_OUTPUT, 2) /* (W9) PRG1_PRU0_GPO13.PRG1_RGMII1_TD2 */

AM64X_IOPAD(0x00f0, PIN_OUTPUT, 2) /* (AA9) PRG1_PRU0_GPO14.PRG1_RGMII1_TD3 */

AM64X_IOPAD(0x00f8, PIN_OUTPUT, 2) /* (V9) PRG1_PRU0_GPO16.PRG1_RGMII1_TXC */

AM64X_IOPAD(0x00f4, PIN_OUTPUT, 2) /* (Y9) PRG1_PRU0_GPO15.PRG1_RGMII1_TX_CTL */

>;

};

/* ETH-B RGMII pin muxing */

icssg1_rgmii2_pins_default: icssg1-rgmii2-default-pins{

pinctrl-single,pins = <

AM64X_IOPAD(0x0108, PIN_INPUT, 2) /* (W11) PRG1_PRU1_GPO0.PRG1_RGMII2_RD0 */

AM64X_IOPAD(0x010c, PIN_INPUT, 2) /* (V11) PRG1_PRU1_GPO1.PRG1_RGMII2_RD1 */

AM64X_IOPAD(0x0110, PIN_INPUT, 2) /* (AA12) PRG1_PRU1_GPO2.PRG1_RGMII2_RD2 */

AM64X_IOPAD(0x0114, PIN_INPUT, 2) /* (Y12) PRG1_PRU1_GPO3.PRG1_RGMII2_RD3 */

AM64X_IOPAD(0x0120, PIN_INPUT, 2) /* (U11) PRG1_PRU1_GPO6.PRG1_RGMII2_RXC */

AM64X_IOPAD(0x0118, PIN_INPUT, 2) /* (W12) PRG1_PRU1_GPO4.PRG1_RGMII2_RX_CTL */

AM64X_IOPAD(0x0134, PIN_OUTPUT, 2) /* (AA10) PRG1_PRU1_GPO11.PRG1_RGMII2_TD0 */

AM64X_IOPAD(0x0138, PIN_OUTPUT, 2) /* (V10) PRG1_PRU1_GPO12.PRG1_RGMII2_TD1 */

AM64X_IOPAD(0x013c, PIN_OUTPUT, 2) /* (U10) PRG1_PRU1_GPO13.PRG1_RGMII2_TD2 */

AM64X_IOPAD(0x0140, PIN_OUTPUT, 2) /* (AA11) PRG1_PRU1_GPO14.PRG1_RGMII2_TD3 */

AM64X_IOPAD(0x0148, PIN_OUTPUT, 2) /* (Y10) PRG1_PRU1_GPO16.PRG1_RGMII2_TXC */

AM64X_IOPAD(0x0144, PIN_OUTPUT, 2) /* (Y11) PRG1_PRU1_GPO15.PRG1_RGMII2_TX_CTL */

>;

};

/* ETH-D RGMII pin muxing */

icssg0_rgmii1_pins_default: icssg0-rgmii1-default-pins{

pinctrl-single,pins = <

AM64X_IOPAD(0x0160, PIN_INPUT, 2) /* (Y1) PRG0_PRU0_GPO0.PRG0_RGMII1_RD0 */

AM64X_IOPAD(0x0164, PIN_INPUT, 2) /* (R4) PRG0_PRU0_GPO1.PRG0_RGMII1_RD1 */

AM64X_IOPAD(0x0168, PIN_INPUT, 2) /* (U2) PRG0_PRU0_GPO2.PRG0_RGMII1_RD2 */

AM64X_IOPAD(0x016c, PIN_INPUT, 2) /* (V2) PRG0_PRU0_GPO3.PRG0_RGMII1_RD3 */

AM64X_IOPAD(0x0178, PIN_INPUT, 2) /* (T3) PRG0_PRU0_GPO6.PRG0_RGMII1_RXC */

AM64X_IOPAD(0x0170, PIN_INPUT, 2) /* (AA2) PRG0_PRU0_GPO4.PRG0_RGMII1_RX_CTL */

AM64X_IOPAD(0x018c, PIN_OUTPUT, 2) /* (Y3) PRG0_PRU0_GPO11.PRG0_RGMII1_TD0 */

AM64X_IOPAD(0x0190, PIN_OUTPUT, 2) /* (AA3) PRG0_PRU0_GPO12.PRG0_RGMII1_TD1 */

AM64X_IOPAD(0x0194, PIN_OUTPUT, 2) /* (R6) PRG0_PRU0_GPO13.PRG0_RGMII1_TD2 */

AM64X_IOPAD(0x0198, PIN_OUTPUT, 2) /* (V4) PRG0_PRU0_GPO14.PRG0_RGMII1_TD3 */

AM64X_IOPAD(0x01a0, PIN_OUTPUT, 2) /* (U4) PRG0_PRU0_GPO16.PRG0_RGMII1_TXC */

AM64X_IOPAD(0x019c, PIN_OUTPUT, 2) /* (T5) PRG0_PRU0_GPO15.PRG0_RGMII1_TX_CTL */

>;

};

/* ETH-E RGMII pin muxing */

icssg0_rgmii2_pins_default: icssg0-rgmii2-default-pins{

pinctrl-single,pins = <

AM64X_IOPAD(0x01b0, PIN_INPUT, 2) /* (Y2) PRG0_PRU1_GPO0.PRG0_RGMII2_RD0 */

AM64X_IOPAD(0x01b4, PIN_INPUT, 2) /* (W2) PRG0_PRU1_GPO1.PRG0_RGMII2_RD1 */

AM64X_IOPAD(0x01b8, PIN_INPUT, 2) /* (V3) PRG0_PRU1_GPO2.PRG0_RGMII2_RD2 */

AM64X_IOPAD(0x01bc, PIN_INPUT, 2) /* (T4) PRG0_PRU1_GPO3.PRG0_RGMII2_RD3 */

AM64X_IOPAD(0x01c8, PIN_INPUT, 2) /* (R5) PRG0_PRU1_GPO6.PRG0_RGMII2_RXC */

AM64X_IOPAD(0x01c0, PIN_INPUT, 2) /* (W3) PRG0_PRU1_GPO4.PRG0_RGMII2_RX_CTL */

AM64X_IOPAD(0x01dc, PIN_OUTPUT, 2) /* (W4) PRG0_PRU1_GPO11.PRG0_RGMII2_TD0 */

AM64X_IOPAD(0x01e0, PIN_OUTPUT, 2) /* (Y4) PRG0_PRU1_GPO12.PRG0_RGMII2_TD1 */

AM64X_IOPAD(0x01e4, PIN_OUTPUT, 2) /* (T6) PRG0_PRU1_GPO13.PRG0_RGMII2_TD2 */

AM64X_IOPAD(0x01e8, PIN_OUTPUT, 2) /* (U6) PRG0_PRU1_GPO14.PRG0_RGMII2_TD3 */

AM64X_IOPAD(0x01f0, PIN_OUTPUT, 2) /* (AA4) PRG0_PRU1_GPO16.PRG0_RGMII2_TXC */

AM64X_IOPAD(0x01ec, PIN_OUTPUT, 2) /* (U5) PRG0_PRU1_GPO15.PRG0_RGMII2_TX_CTL */

>;

};

&icssg0_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&icssg0_mdio1_pins_default>;

icssg0_phy1: ethernet-phy@f {

reg = <0xf>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

icssg0_phy2: ethernet-phy@3 {

reg = <0x3>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

&icssg1_mdio {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&icssg1_mdio1_pins_default>;

icssg1_phy1: ethernet-phy@f {

reg = <0xf>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

icssg1_phy2: ethernet-phy@3 {

reg = <0x3>;

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

&cpsw3g {

bootph-all;

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&rgmii1_pins_default>;

/* Map HW8_TS_PUSH to GENF1 */

cpts@3d000 {

ti,pps = <7 1>;

};

};

&cpsw_port1 {

status = "okay";

bootph-all;

phy-mode = "rgmii-rxid";

phy-handle = <&cpsw3g_phy0>;

};

&cpsw_port2 {

status = "disabled";

bootph-all;

phy-mode = "rgmii-rxid";

};

&cpsw3g_mdio {

bootph-all;

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&mdio1_pins_default>;

cpsw3g_phy0: ethernet-phy@3 {

bootph-all;

reg = <3>;

local-mac-address = [1C 63 49 1A DE 19];

ti,rx-internal-delay = <DP83867_RGMIIDCTL_2_00_NS>;

ti,fifo-depth = <DP83867_PHYCR_FIFO_DEPTH_4_B_NIB>;

};

};

mdio1_pins_default: mdio1-default-pins {

bootph-all;

pinctrl-single,pins = <

AM64X_IOPAD(0x01fc, PIN_OUTPUT, 4) /* (R2) PRG0_PRU1_GPO19.MDIO0_MDC */

AM64X_IOPAD(0x01f8, PIN_INPUT, 4) /* (P5) PRG0_PRU1_GPO18.MDIO0_MDIO */

>;

};

rgmii1_pins_default: rgmii1-default-pins {

bootph-all;

pinctrl-single,pins = <

AM64X_IOPAD(0x011c, PIN_INPUT, 4) /* (AA13) PRG1_PRU1_GPO5.RGMII1_RD0 */

AM64X_IOPAD(0x0128, PIN_INPUT, 4) /* (U12) PRG1_PRU1_GPO8.RGMII1_RD1 */

AM64X_IOPAD(0x0150, PIN_INPUT, 4) /* (Y13) PRG1_PRU1_GPO18.RGMII1_RD2 */

AM64X_IOPAD(0x0154, PIN_INPUT, 4) /* (V12) PRG1_PRU1_GPO19.RGMII1_RD3 */

AM64X_IOPAD(0x00d8, PIN_INPUT, 4) /* (W13) PRG1_PRU0_GPO8.RGMII1_RXC */

AM64X_IOPAD(0x00cc, PIN_INPUT, 4) /* (V13) PRG1_PRU0_GPO5.RGMII1_RX_CTL */

AM64X_IOPAD(0x0124, PIN_OUTPUT, 4) /* (V15) PRG1_PRU1_GPO7.RGMII1_TD0 */

AM64X_IOPAD(0x012c, PIN_OUTPUT, 4) /* (V14) PRG1_PRU1_GPO9.RGMII1_TD1 */

AM64X_IOPAD(0x0130, PIN_OUTPUT, 4) /* (W14) PRG1_PRU1_GPO10.RGMII1_TD2 */

AM64X_IOPAD(0x014c, PIN_OUTPUT, 4) /* (AA14) PRG1_PRU1_GPO17.RGMII1_TD3 */

AM64X_IOPAD(0x00e0, PIN_OUTPUT, 4) /* (U14) PRG1_PRU0_GPO10.RGMII1_TXC */

AM64X_IOPAD(0x00dc, PIN_OUTPUT, 4) /* (U15) PRG1_PRU0_GPO9.RGMII1_TX_CTL */

>;

};

Hello TI,

We are using AM6442BSDHAALV as the processor (MAC) and DP83869HM as PHY.

In our design we have 5 Ethernet ports connected from AM6442BSDGHAALV to DP838369 and then to the RJ45 with Inbuilt Magnetics. We are sharing 3 MDC, MDIO lines with 5 DP83869 PHY. RGMII Interface connectivity block diagram is attached for your reference.

The block diagram for the MDC/MDIO interface is also attached for your reference.

Our operating mode is RGMII to Copper (1000 BASE-T, 100 BASE-TX, 10 BASE-TE).

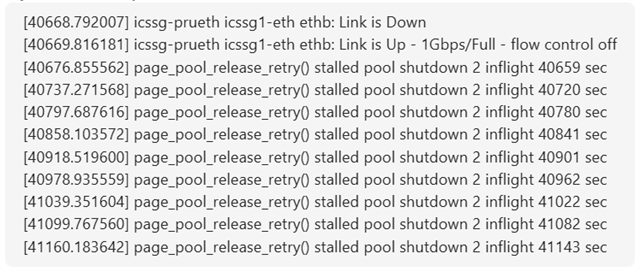

The problem statement is, with the above configuration we are facing the Ethernet Link Instability issue, which means the Ethernet Link is down and up often and randomly. Hereby attaching the Debug logs for your reference.

Also attaching the Device Tree configuration for your reference.

Note: We are facing the Link Instability issue (i,e.: Link Down / Link Up) in ICSSG0 & ICSSG1 Core only.

Can you please help us to proceed further.

Thank you.

Regards

Amarnath G