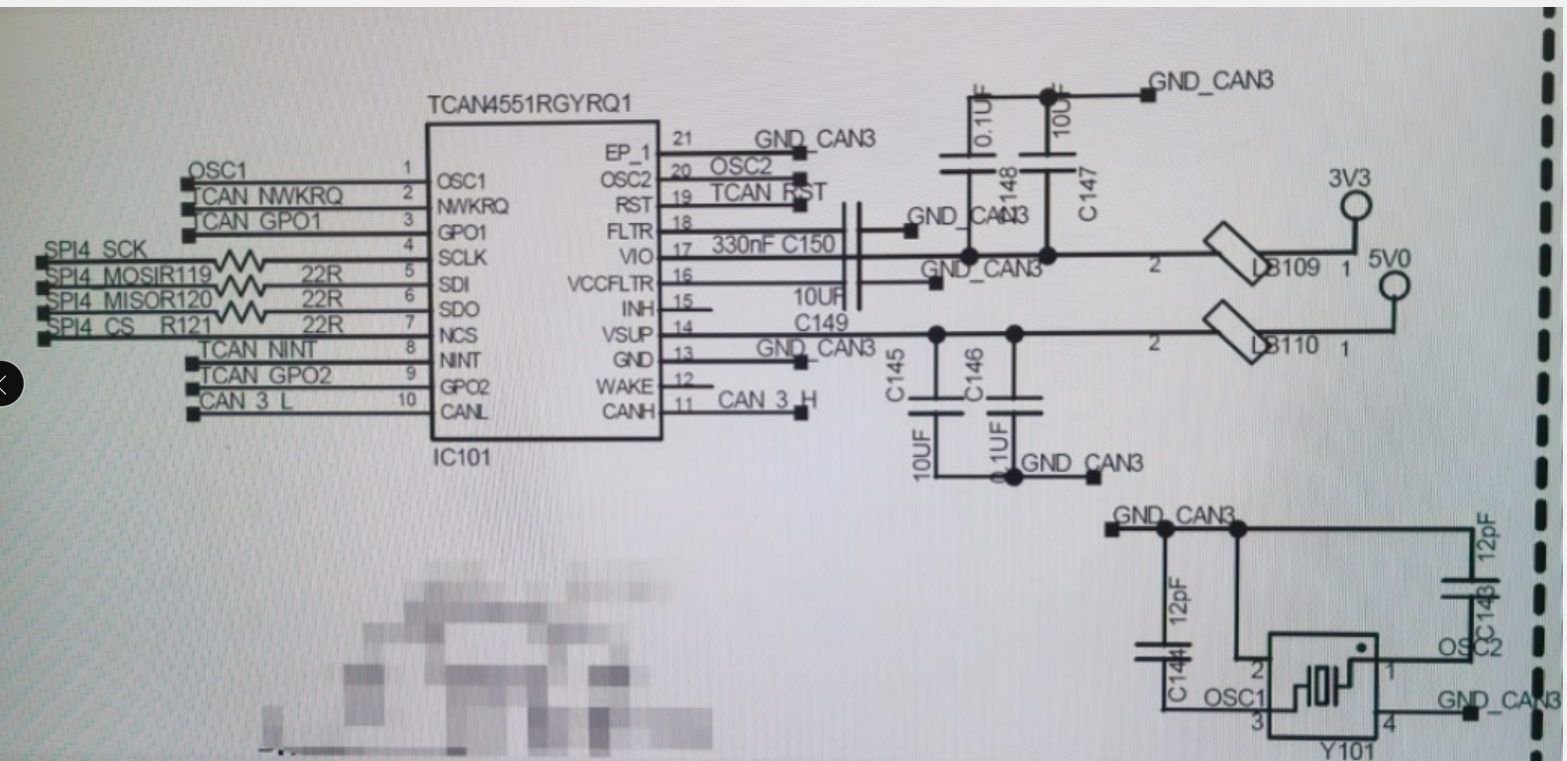

Part Number: TCAN4551-Q1

Hi Team,

Could you please help to check the following schematic and share your comments? Is it necessary to add 40M crystal oscillator on TCAN4551-Q1 application? Besides, if we want to read the device ID, any special action need to take or just follow SPI read is okay?

Thanks.

BRs.

Frank