Other Parts Discussed in Thread: DSI-TUNER

We are using the SN65DSI840Q1 chip as a bridge from MIPI to LVDS on MTK Genio-510.

However, it's not working properly, so we need some help to check if the device tree is incorrect.

display_overlay.dts

/dts-v1/;

/plugin/;

#include <dt-bindings/pinctrl/mediatek,mt8188-pinfunc.h>

#include <dt-bindings/interrupt-controller/irq.h>

#include <dt-bindings/gpio/gpio.h>

/ {

fragment@0 {

target = <&i2c5>;

__overlay__ {

sn65dsi84: sn65dsi84@2d {

compatible = "ti,sn65dsi84";

reg = <0x2d>;

enable-gpios = <&pio 11 GPIO_ACTIVE_HIGH>;

// interrupts-extended = <&pio 6 IRQ_TYPE_LEVEL_LOW>;

pinctrl-names = "default";

pinctrl-0 = <&sn65_pins>;

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

sn65_dsi_in: endpoint {

remote-endpoint = <&dsi0_out>;

data-lanes = <0 1 2>;

};

};

port@2 {

reg = <2>;

bridge_out_a: endpoint {

remote-endpoint = <&panel_in_a>;

};

};

port@3 {

reg = <3>;

bridge_out_b: endpoint {

remote-endpoint = <&panel_in_b>;

};

};

};

};

};

};

fragment@1 {

target = <&dsi0>;

__overlay__ {

panel@0 {

status = "disabled";

};

/delete-node/ ports;

ports {

port {

dsi0_out: endpoint {

remote-endpoint = <&sn65_dsi_in>;

data-lanes = <0 1 2>;

};

};

};

};

};

fragment@2{

target = <&lcm1_tp_avdd>;

__overlay__ {

status = "disabled";

};

};

fragment@3 {

target = <&i2c0>;

__overlay__ {

touchscreen@5d {

status = "disabled";

};

};

};

fragment@4 {

target = <&dpi1>;

__overlay__ {

status = "disabled";

};

};

fragment@5 {

target = <&hdmi0>;

__overlay__ {

status = "disabled";

};

};

fragment@6 {

target = <&hdmi_phy>;

__overlay__ {

status = "disabled";

};

};

fragment@7 {

target = <&cec>;

__overlay__ {

status = "disabled";

};

};

fragment@8 {

target = <&sound>;

__overlay__ {

dai-link-1 { /* HDMI */

status = "disabled";

};

dai-link-2 { /* DPTX */

status = "disabled";

};

};

};

fragment@9 {

target = <&backlight_lcd0>;

__overlay__ {

status = "okay";

default-on;

power-supply = <&edp_panel_fixed_3v3>;

enable-active-high;

};

};

fragment@10 {

target = <&disp_pwm0>;

__overlay__ {

status = "okay";

pinctrl-names = "default";

pinctrl-0 = <&disp_pwm0_pin_default>;

};

};

fragment@11 {

target = <&pio>;

__overlay__ {

disp_pwm0_pin_default: disp-pwm0-pin-default {

pins1 {

pinmux = <PINMUX_GPIO29__FUNC_O_DISP_PWM0>;

};

};

sn65_pins: sn65-pins {

sn65_en: pin-en {

pinmux = <PINMUX_GPIO11__FUNC_B_GPIO11>;

output-high;

};

};

lvds_bk_en_high: lvds-bk-en-high {

pins2 {

pinmux = <PINMUX_GPIO8__FUNC_B_GPIO8>;

output-high;

};

};

};

};

fragment@12 {

target-path = "/";

__overlay__ {

panel_lvds: panel-lvds {

compatible = "panel-lvds";

power-supply = <&edp_panel_fixed_3v3>;

backlight = <&backlight_lcd0>;

status = "okay";

width-mm = <344>;

height-mm = <193>;

data-mapping = "vesa-24";

dual-link;

panel-timing {

clock-frequency = <74250000>;

hactive = <1920>;

vactive = <1080>;

hback-porch = <148>;

hfront-porch = <88>;

vback-porch = <36>;

vfront-porch = <4>;

hsync-len = <44>;

vsync-len = <5>;

};

ports {

#address-cells = <1>;

#size-cells = <0>;

port@0 {

reg = <0>;

dual-lvds-odd-pixels;

panel_in_a: endpoint {

remote-endpoint = <&bridge_out_a>;

};

};

port@1 {

reg = <1>;

dual-lvds-even-pixels;

panel_in_b: endpoint {

remote-endpoint = <&bridge_out_b>;

};

};

};

};

};

};

fragment@13 {

target = <&edp_panel_fixed_3v3>;

__overlay__ {

regulator-state-mem {

regulator-on-in-suspend;

};

};

};

};

After applying the display_overlay on the board we got the follow dmesg, althrough the SN65DSI84 driver is probed.

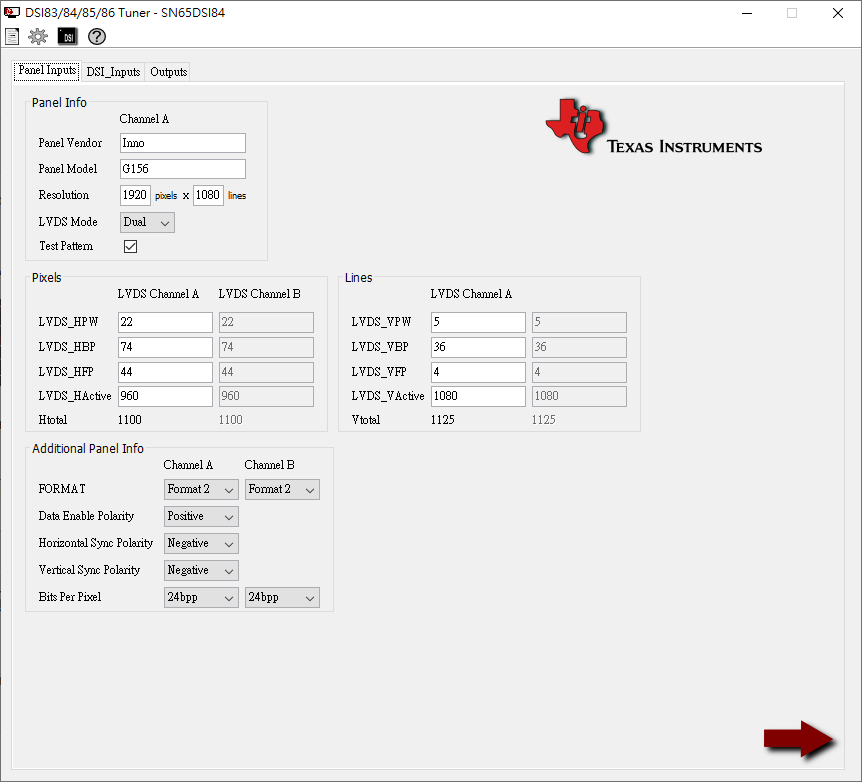

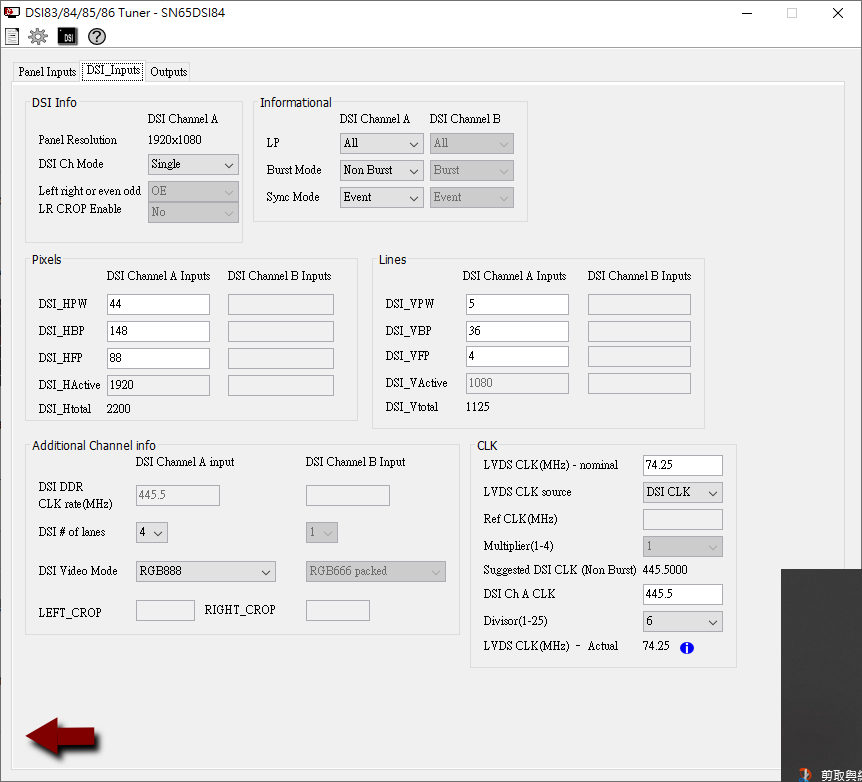

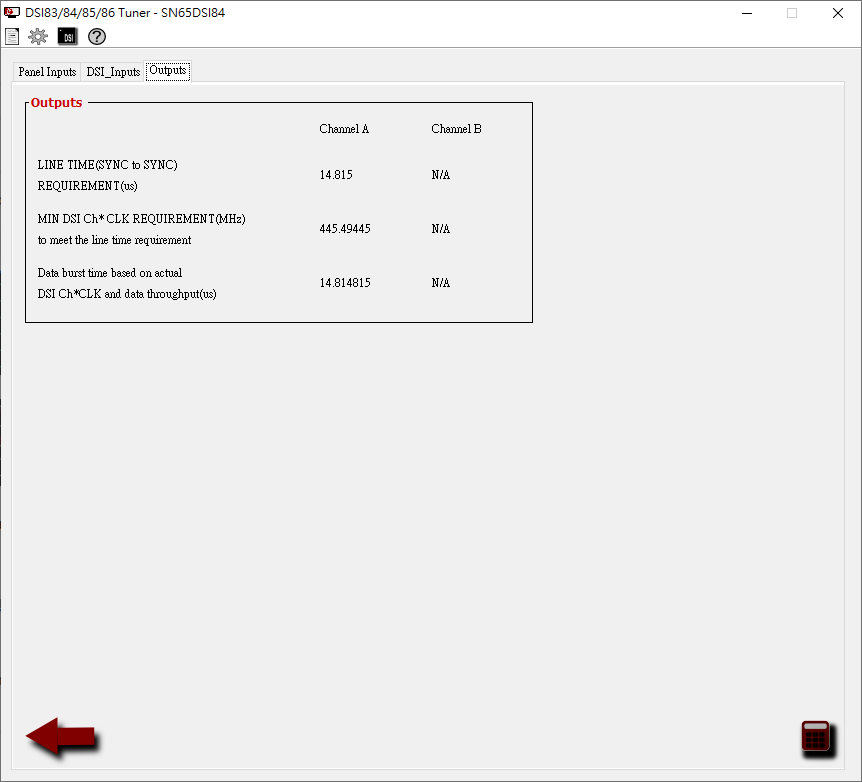

We tried to output the test pattern and set the DSI-TUNER value as below. After getting the CSR values, we tested CSR values using i2ctranfer command to write the register but it still output nothing.