Part Number: DP83826AE

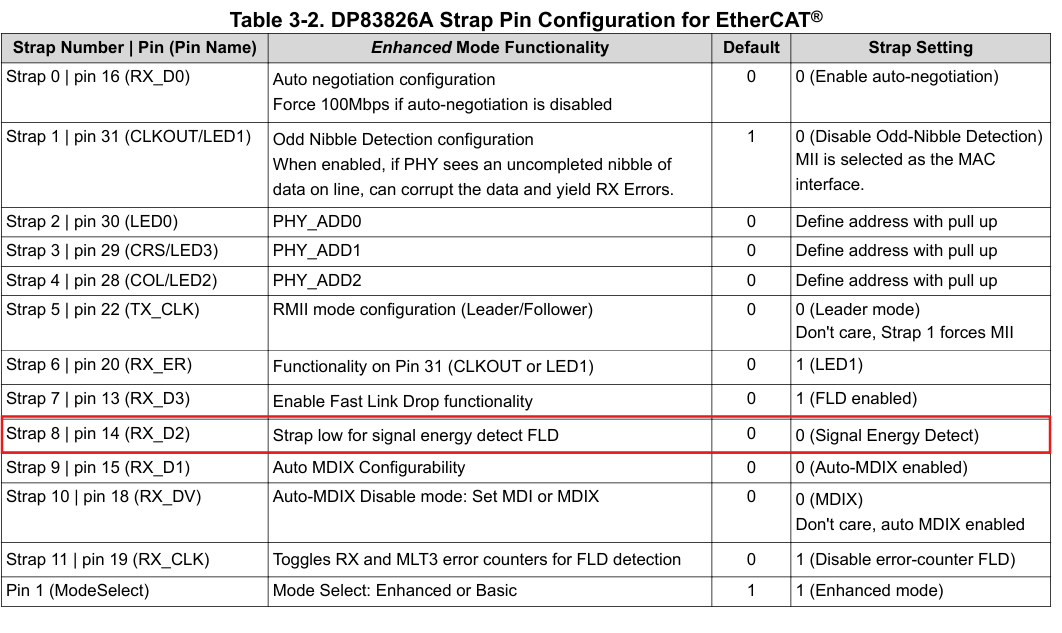

The strap configuration according to datasheet mentiones that "For EtherCAT applications or applications with Fast link drop enabled and expect to handle Baseline wander packets, recommend disable signal energy detect, which can be done by setting Strap8 "

1) This implies from flowchart Strap 1=0(MII, odd nibble disable), strap7(FLD enable)=1 (This is clear)

2) Now application note schematic implements 1* strapping along with Strap8=1(go to strap 11) and strap 11=1(disable error-counter FLD)

This doesnt match with the table provided in application note for strapping where strap8 is suggested to be set to 0(Energy signal enable)

Can you confirm what should be the strapping for EtherCAT with FLD enable, Energy detect disable wrt Strap 8.

Also is the configuration given in application note for Ethercat implementation makes sure FLD is enabled? becaure initially on Strap 7 we enable FLD but again in strap 11 it is mentioned FLD is disabled

Is the following flowchart correct for ethercat implementation for DP83826AE