Hello,

Please support of customer question for LMH0340 and refer to the below.

1.Customer request of FPGA IP source, Verilog and VHDL formats .

Refer to the site and description from TI.

>http://www.ti.com/tool/sdxilevk,

>TI FPGA IP

The FPGA IP is available for download as a SRAM Object File (SOF) file. Texas Instruments provides synthesizable FPGA source code in both Verilog and VHDL formats. Please contact your local TI representative to obtain a login and password to the FPGA IP FTP site.

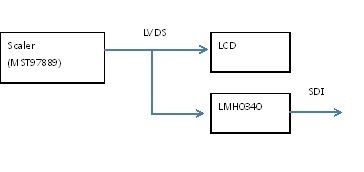

2. Other customer block and I’d like to receive your comment.

She want to use from LVDS to SDI of LMH0340.

I think, This Block is available operation, but customer board is not working and LCD display is OK.

I check, /LOCK(pin,31) is Active Low is normal, but customer bd is high.

IF you have any comment and others to control the LMH0340, please let me know it.(ex.Software setting or register setting,,)

Attached schematic

From Avnet-korea / Eddy

Eddy.lee@avnet.com