When are the input audio samples that received at the I2S pins captured?

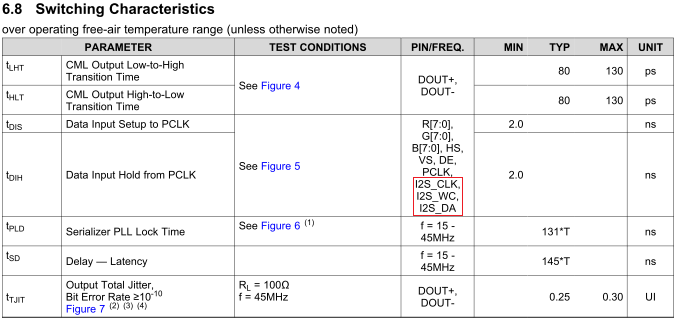

In the datasheet the setup and hold times to/from PCLK for the data input including the I2S pins (I2S_CLK, I2S_WC, I2S_DA) are defined. Does this mean that the input audio samples are captured on the edge of the PCLK?

Our customer is concerned that the input audio samples which are not synchronized to PCLK cannot be captured correctly.

Best regards,

Daisuke