Other Parts Discussed in Thread: TEST2,

Hi Sirs,

My customer have try to disable ASSR_control register. (refer https://e2e.ti.com/support/interface/digital_interface/f/130/t/542842)

But, they still failed to let their target panel work with SN65DSI86EVM.

Do you have any advices let us to fix my customer's issue. Thanks!

Please refer below info by my customer provided.

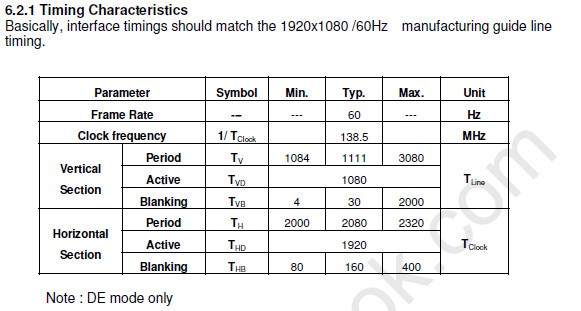

1. The below is the panel timing has ever enabled our target panel to work in other bridge IC( LVD-to-eDP bridge )

Resolution = 1920x1080

vertical_sync_active = 2

vertical_backporch = 4

vertical_frontporch = 2

horizontal_sync_active = 18

horizontal_backporch = 50

horizontal_frontporch = 50

2. The panel does not support ASSR mechanism.

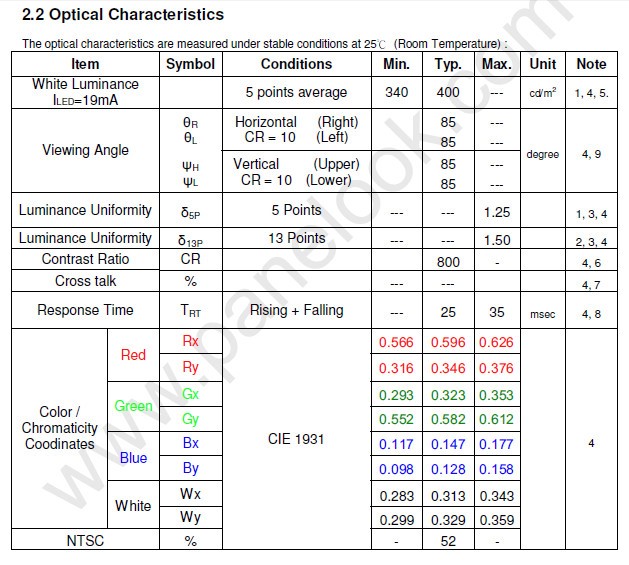

3. The data format input to the panel is RGB 666.