Dears,

I am the FAE of MarubunArrow7268.DSI83-Q1 problem.xlsx

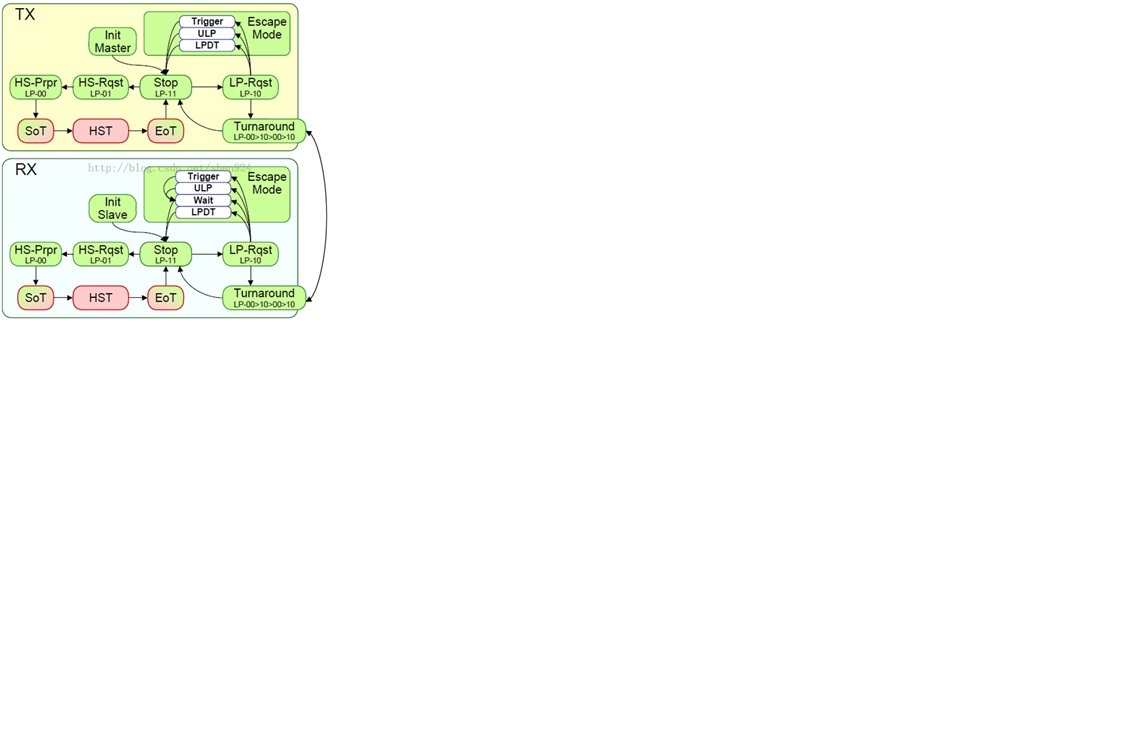

my customer use SN65DSI83-Q1 to convert MIPI to LVDS(LCD display), now it can display with test pattern, but no display with DSI input. the 0xE5 register data is 0x09.

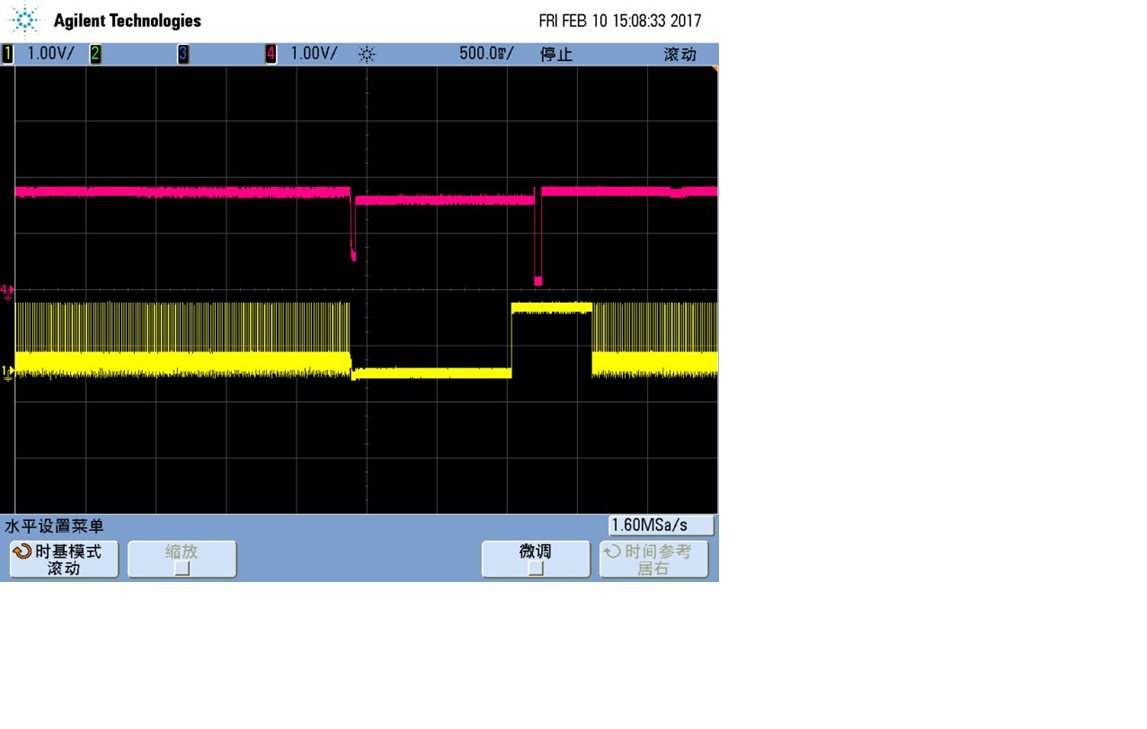

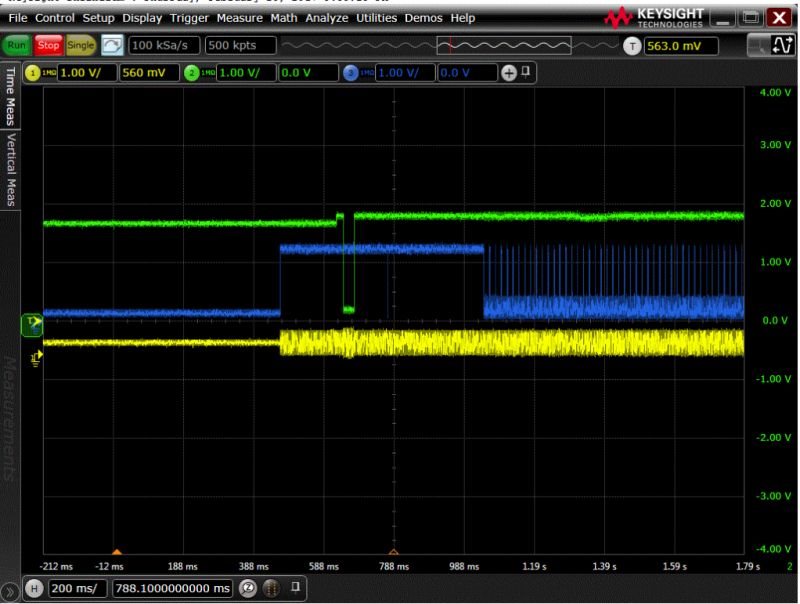

we check the initial sequence, it can meet Datasheet, and we also check the DSI input clock, it is OK.

our customer use another vendor's IC in the same board, it can display correctly.

enclose is the waveform, setting and register data.

I want to know which problem will make the error: 0x09, and how to solve it? please provide you suggestion.--Thank you