Part Number: TLK10232

Hi Team,

My customer is facing the issue that FPGA is stuck sometime when issuing Data path reset on TLK10232. As far as we check the FPGA error status, it seems that FPGA gets Alignment error at XAUI line at the timing and can not sync again due to some reason.

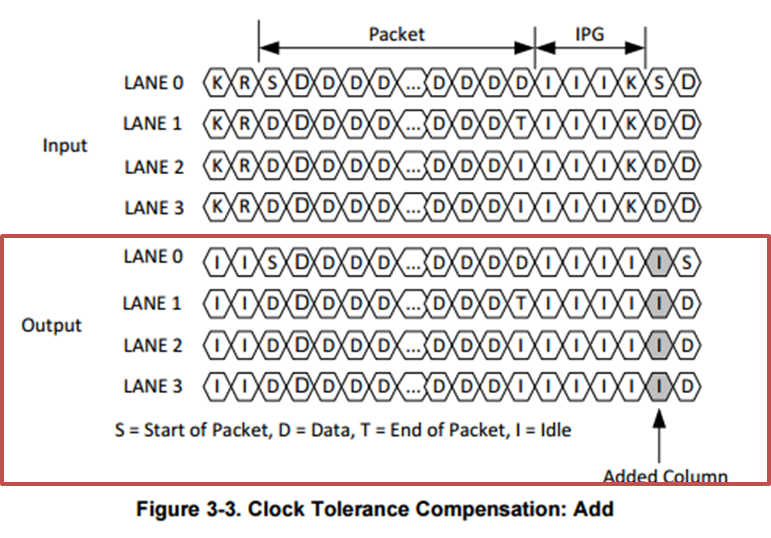

According to datasheet, TLK10232 automatically converts /A/, /K/ and /R/ character to Idle and outputs "Idle" pattern only(between data packet) on XAUI line continuously as default. We are guessing that this might be root cause of this issue.

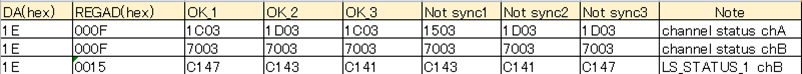

Are there any registers to issue the characters for XAUI lane alignment?

The customer is using TLK10232 in 10G KR mode, so FORCE_LM_REALIGN register change doesn't work because this register is only for 10G-KX mode.

(I think that PCS_RX_DEC_CTRL_CHAR may be used, so please let me know if you know how this register behaves. )

Regards,

Takashi Onawa