Hi everyone,

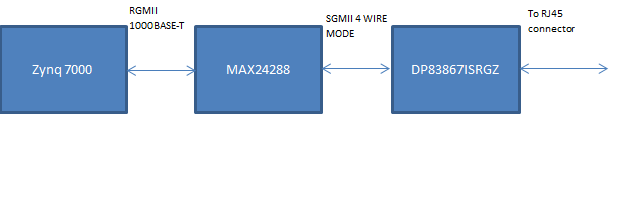

I'm working on Zynq platform. I have tested RGMII mode on DP83867ISRGZ.

Now working with MAX24288 parallel to serial converter.

Auto-negotiation for DP83867 speed is completing with 1000Mbps.

but the SGMII Auto-negotiation with MAX24288 is not passing.

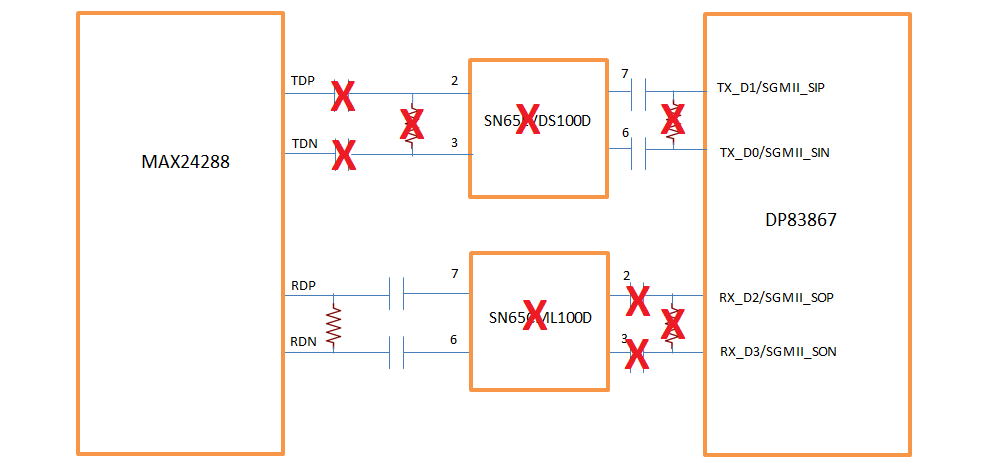

There is a level translator CML to LVDS between MAX and DP83867.

I have followed same sequence for configuration of DP83867 as RGMII. except

Register 0x10 SGMII enable

0xD3 for SGMII 4 wire mode

and Auto-negotiation speed advertise for 1000, 100 and 10Mbps

here Auto-negotiation is passing and then SGMII Auto-negotiation is enabled

here it is not completing SGMII Auto-negotiation.

I've shared the communication diagram.

Please suggest if anything missing and also the steps to be followed.

Thanks in advance.

Regards,

Sukanya K