Other Parts Discussed in Thread: DS90UH948-Q1, ALP

Hi,

For our custom display solution, we are using the below serdes pair

Serializer : DS90UB921-Q1

Deserializer : DS90UH948-Q1

Display timings are configured properly in the kernel.

But we do not get anything up on the display.

serdes lock is established.

Serializer test patterns and deserializer test patterns also do not work with external clock timings.

Work-around:

If we run serializer pattern with internal clock, then we see that the pattern is coming on the display.

Later if we disable the pattern, then our HMI is up on the display.

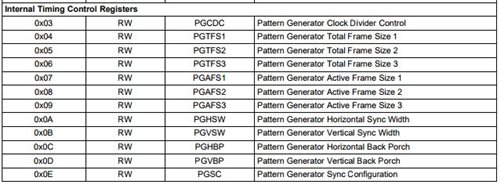

Need support here to understand what configuration is set on serializer/de-serializer when we set the internal clock pattern ?

Note : we see only register 0x3B getting updated on deserializer side between working and non-working scenarios. This register has no mention in datasheet, seems to be reserved one.