Other Parts Discussed in Thread: AM4377, , DP83640

Hi,

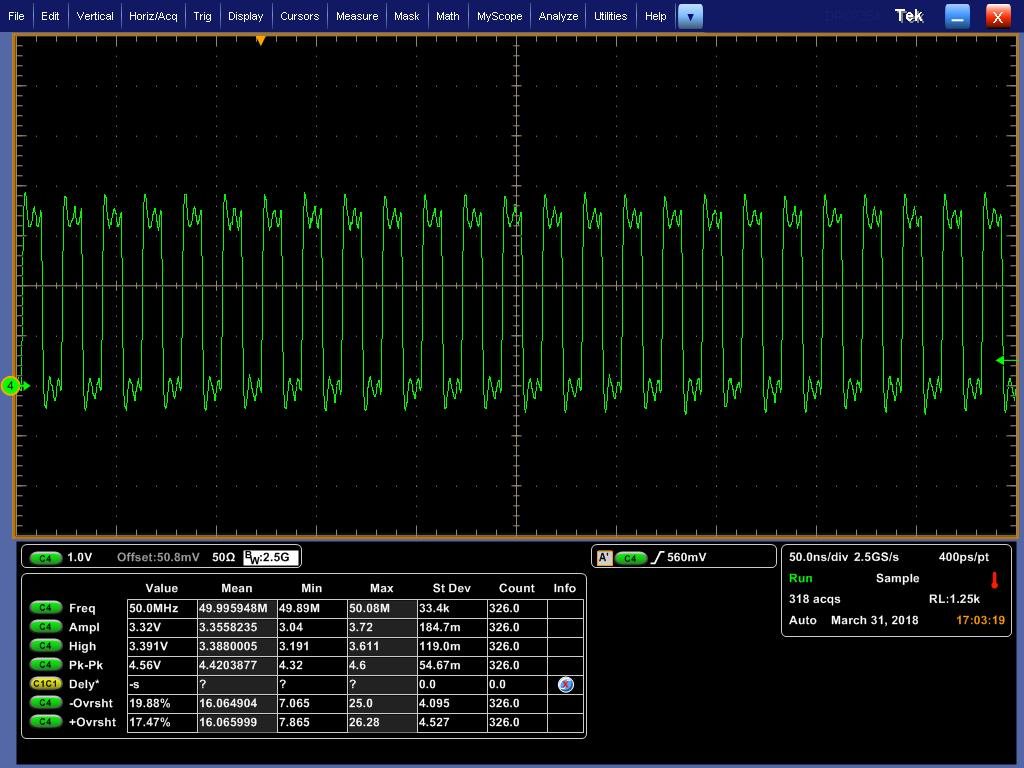

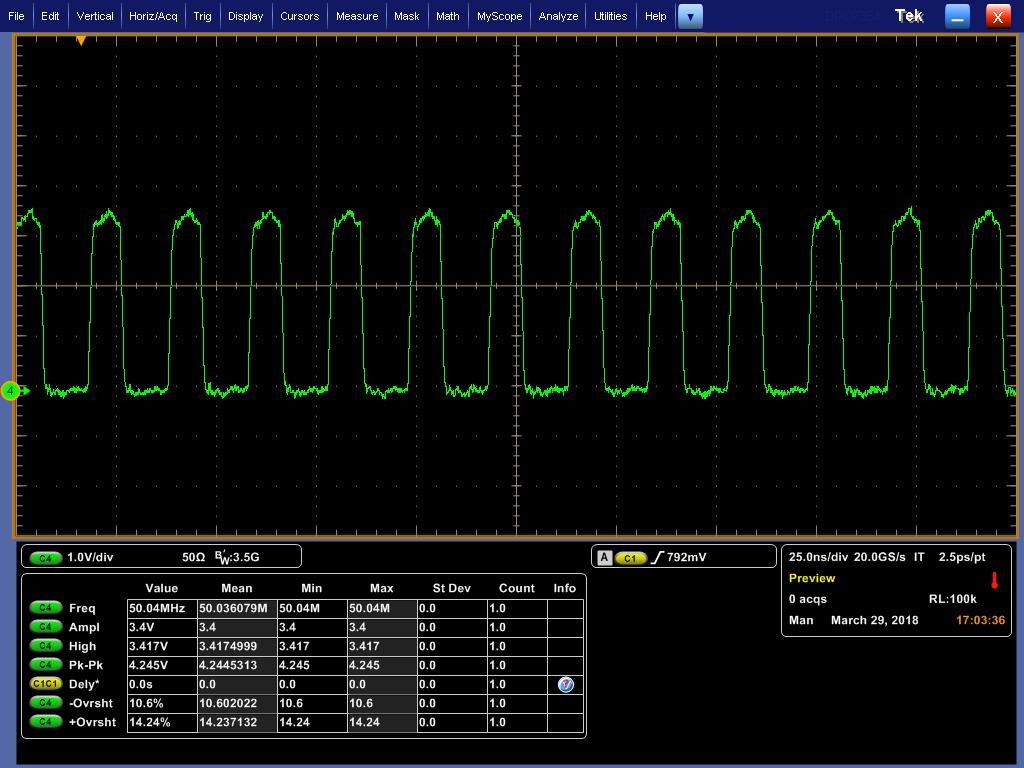

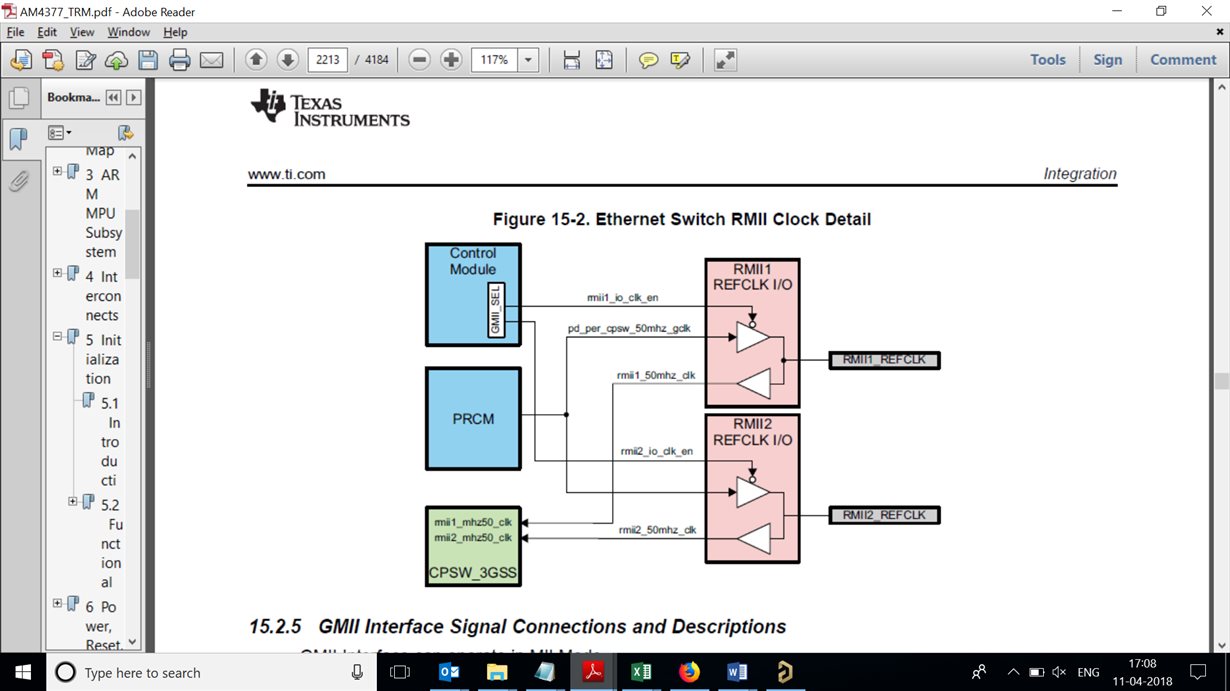

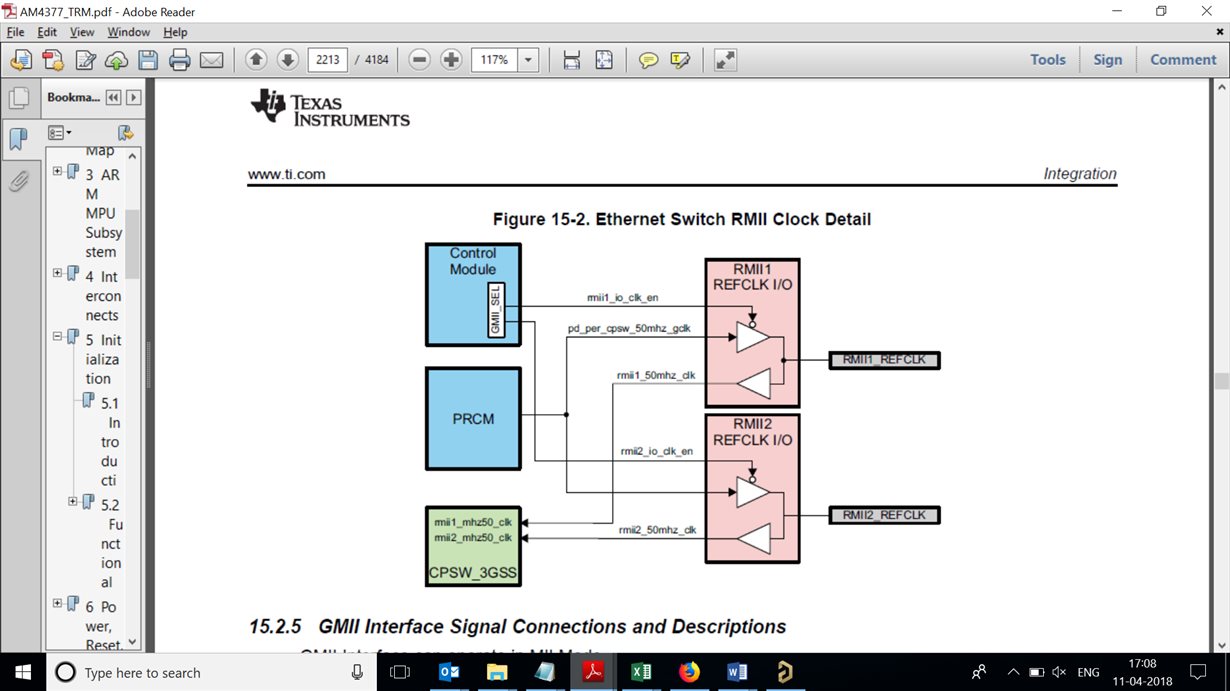

We are using TI's AM4377 CPU and DP83620 Ethernet PHY in one of our projects. We are able to make 10 Mbps up, but with 100 Mbps there is around 30-60% packet loss. Our test set-up is as below.

AM4377 CPU located in the main PCB and DP83620 Ethernet PHY in the communication PCB. CPU/MAC to PHY connection is through Samtec card edge connector (PN: HSEC8-120-01-SM-DV-A). Attached Ethernet PHY board schematics herewith. The trace lengths are within DP83620 PHY guidelines (< 6 inches as in 'AN-1469 PHYTER Design & Layout Guide'). Attached Trace length details as well.

Also, please find few more queries:

- Please let us know the strap option for TX

6558.ETHERNET_LENGTH_MATCH_ANALYSIS_TI.xlsxD_3 pin (to enable RMII Slave mode), as it is not clear from datasheet.

6558.ETHERNET_LENGTH_MATCH_ANALYSIS_TI.xlsxD_3 pin (to enable RMII Slave mode), as it is not clear from datasheet. - Request your suggestion in finding the right termination value for these trace lengths and any other recommendations if any (other than termination resistor).

- We did not get any errata sheet for the PHY chip. Please help on this as well.

Best Regards,

Madhusoodana Bairy