Other Parts Discussed in Thread: DP83630

Hi Team,

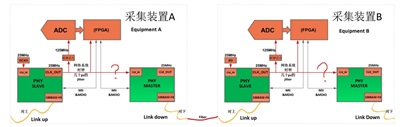

My customer is looking for PHY support IEEE1588, we penetrated DP83640. I got a question want to check with expert about the application note AN-1728:

Question is that what is the red circle I highlighted in the picture mean? Is it is CLK_OUT of the two DP83640 showed in the picture?

If customer use DP83640 in two different equipment which are far way from each other(May up to several kilometers), so how to sync the clock or sync the clock?

Another question is in order to sync the two equipment less than 10ns, any guidelines for customer to refer?

Thanks for the support?

Best regards,

Sulyn