Other Parts Discussed in Thread: PCA9555

Hi Sirs,

One more question.

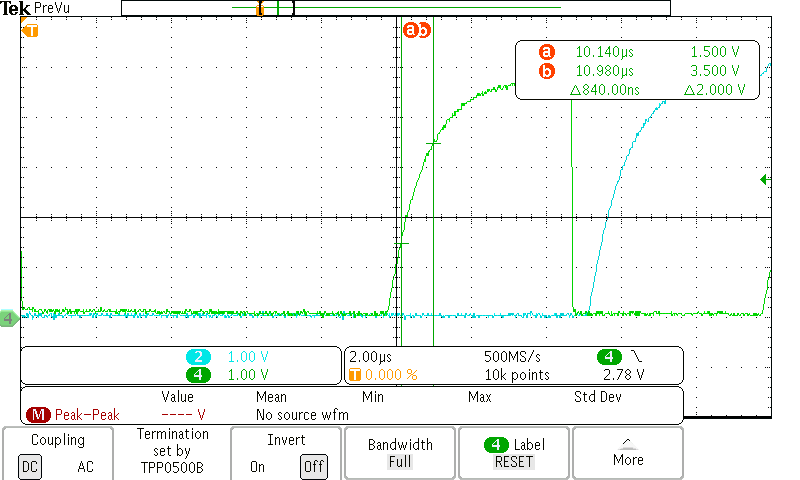

May i know what is your test condition on datasheet of I2C input rise time??

The value is show 1000ns max, but we use 800ns the BMC will send fail message.

So, we would like to know what is the test condition .

Thanks!!