Other Parts Discussed in Thread: LMH0031, , THS8200, TVP7002

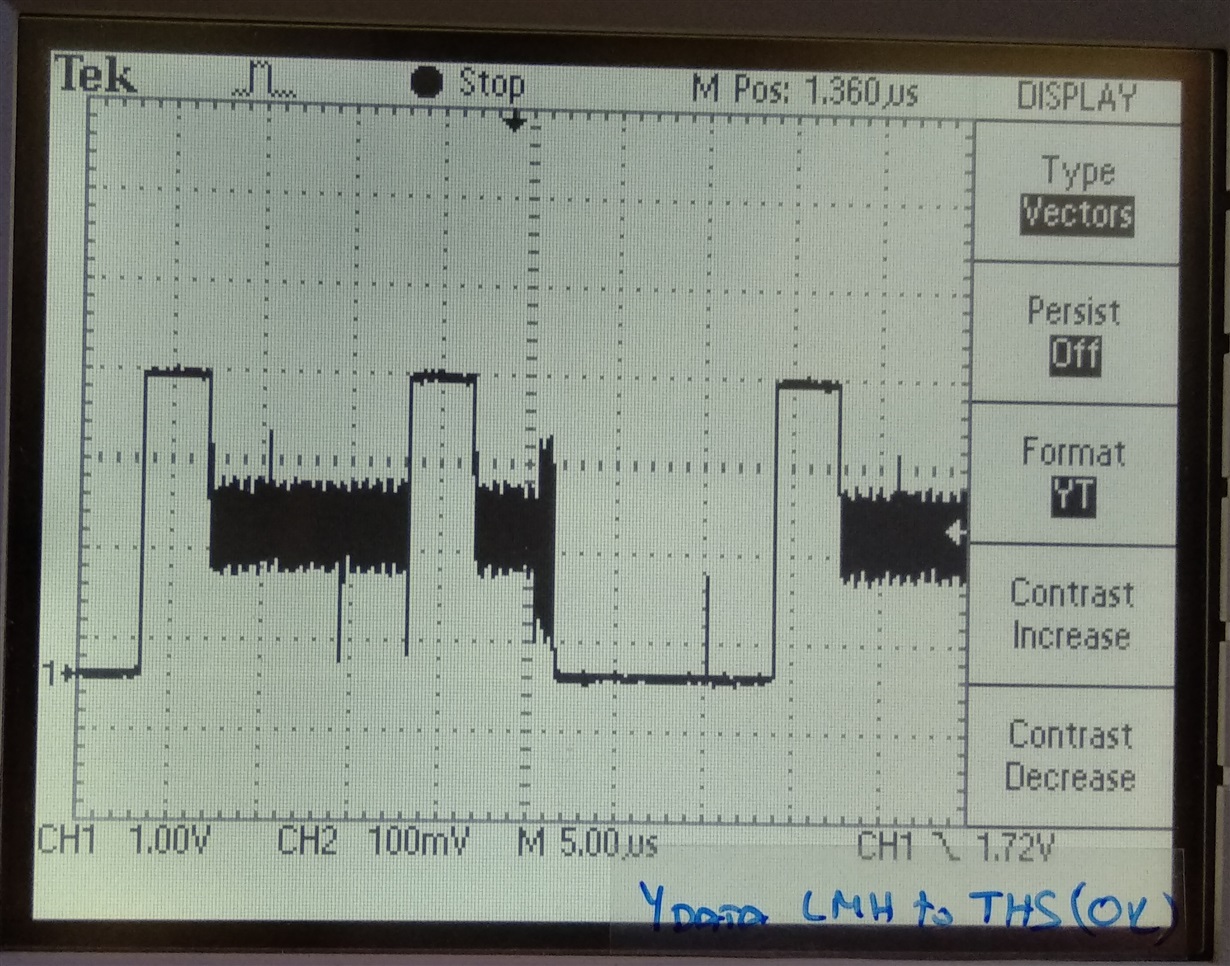

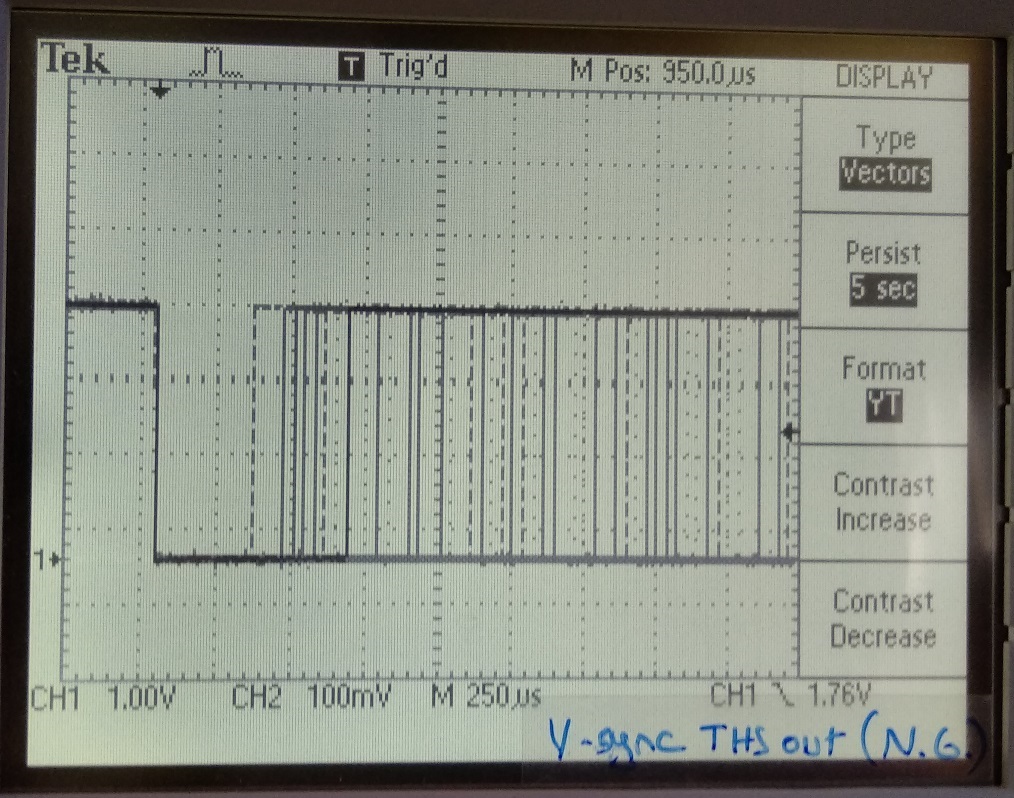

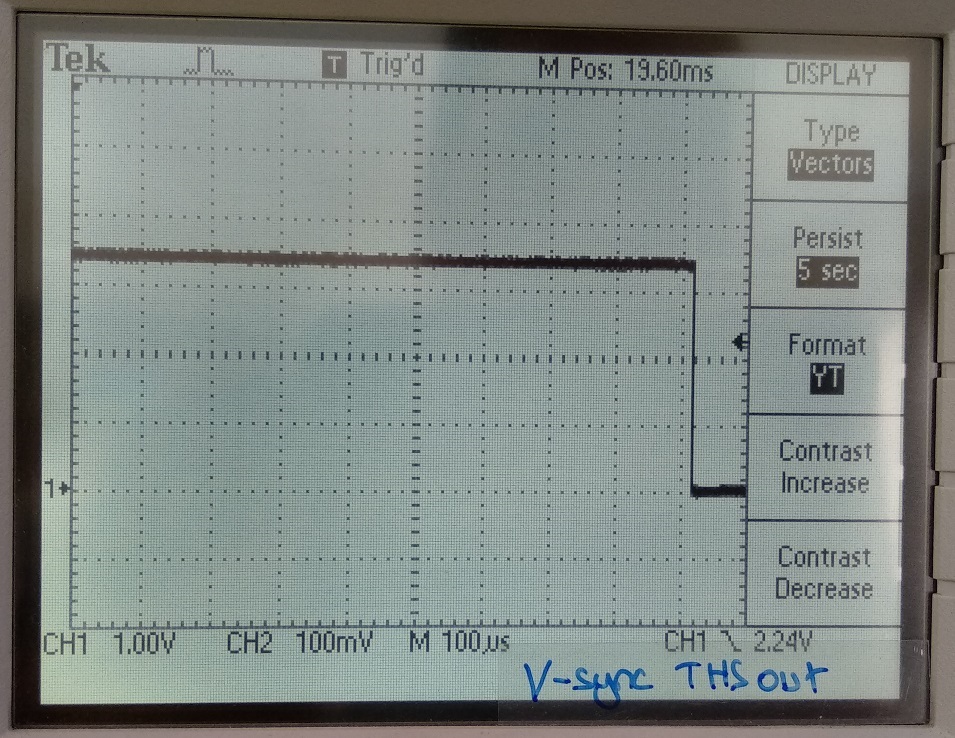

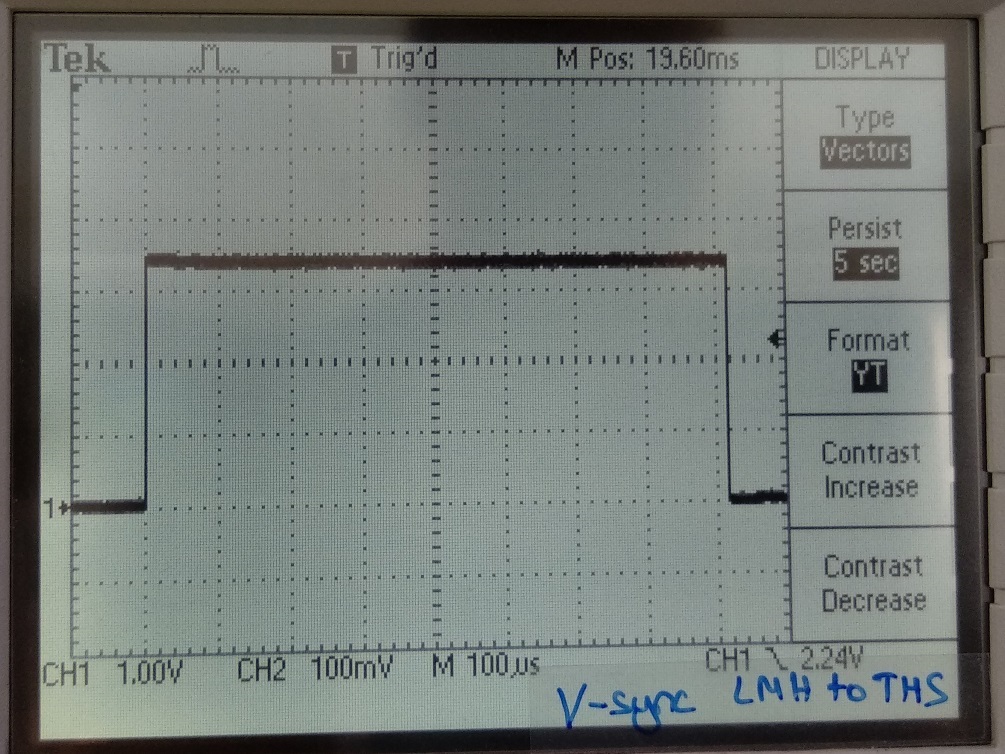

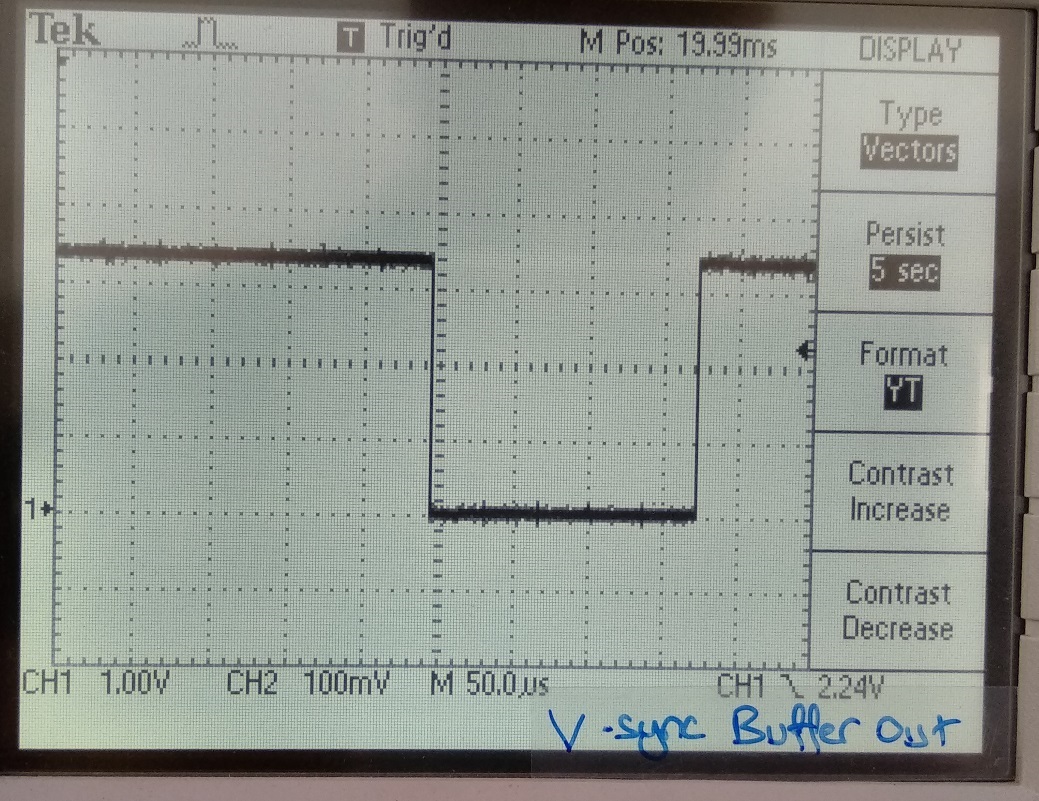

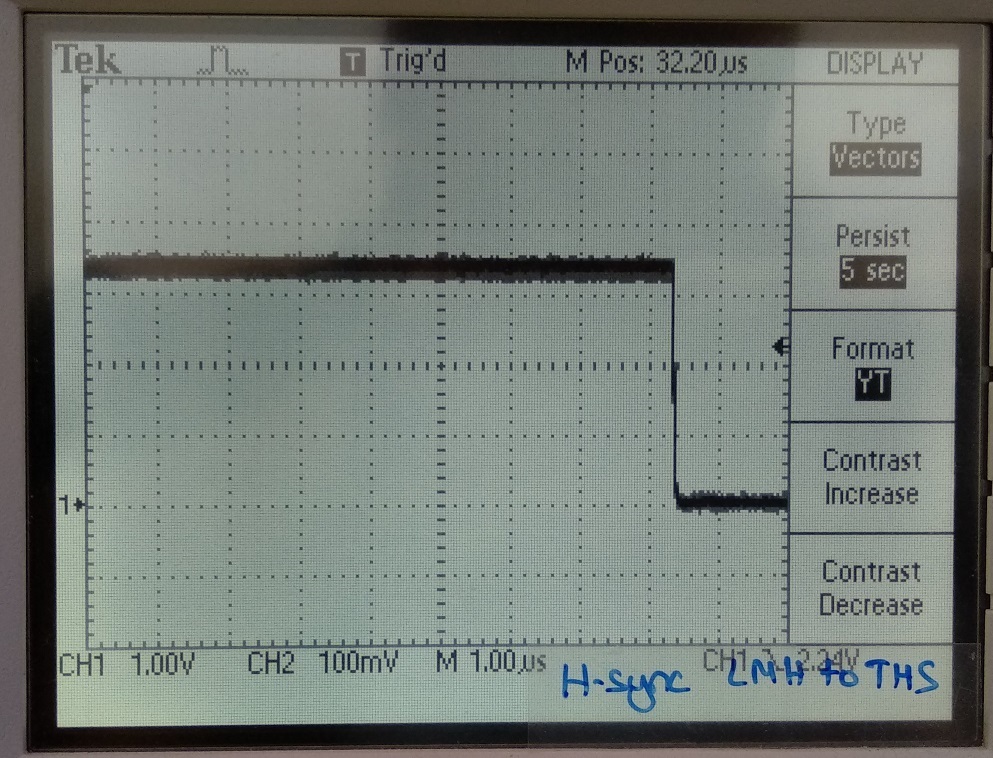

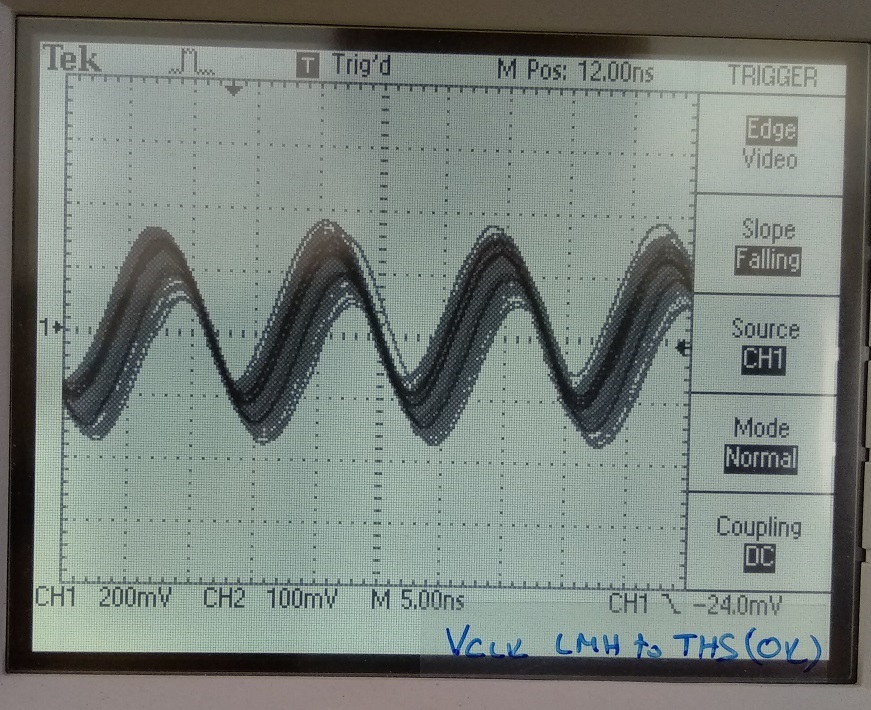

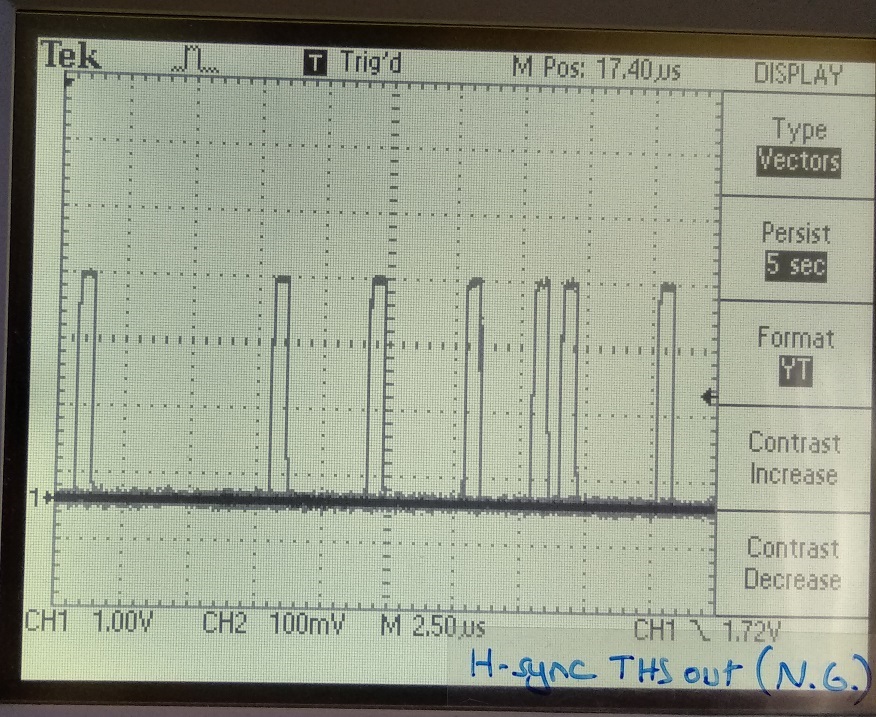

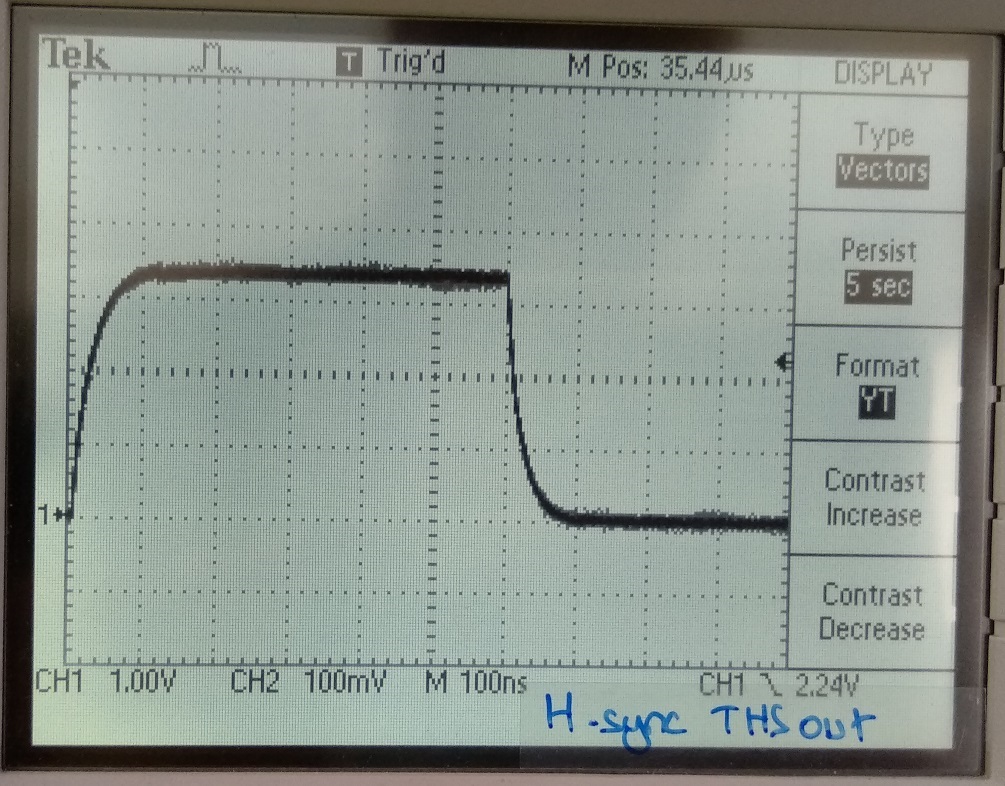

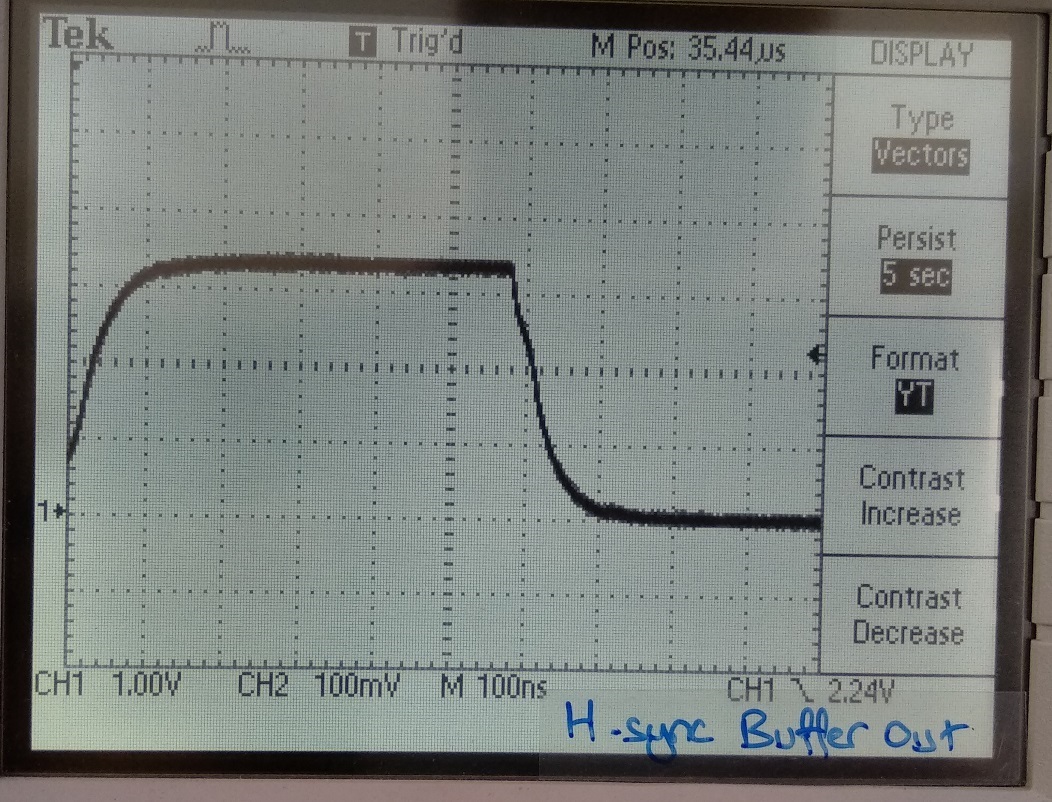

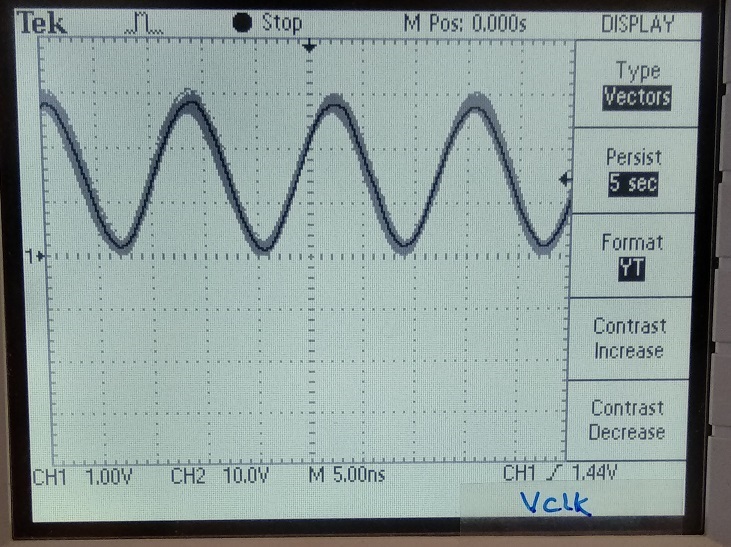

I working on a HDSDI to VGA converter project. VGA monitor does not sense the input format due to irregular Hsync or Vsync pulses. RBG ADC ouputs are Ok. Hsync out and/or Vsync out does not locked to input signal always. Problem occurs randomly, when it is locked it keeps running correctly untll input signal change or power on-off.The source to THS8200-EP is LMH0031 . 20bit Video data , HS,VS , F are connected to THS8200-EP. Both setting DS and ES has same results. HS and VS from LMH0031 is ok always.