Part Number: TCAN4550-Q1

Other Parts Discussed in Thread: TCAN4550

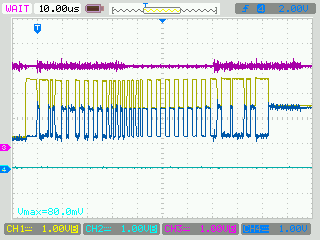

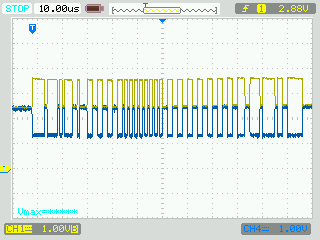

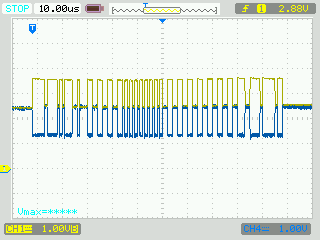

I’m setting up two TCAN4550 modules to send messages back and forth but I’m having a problem with the Transmit operation. I'm trying to send a Standard ID CAN message with 32bytes of data. I was expecting to see a single transmission with a length of ~290us but what I’m seeing is a repeated 67us length transmission. This transmission gets repeated every 91.6us. I've attached a Word document that shows my setup along with some oscilloscope captures that show the transmissions.

Thanks,

Joe