Hi,

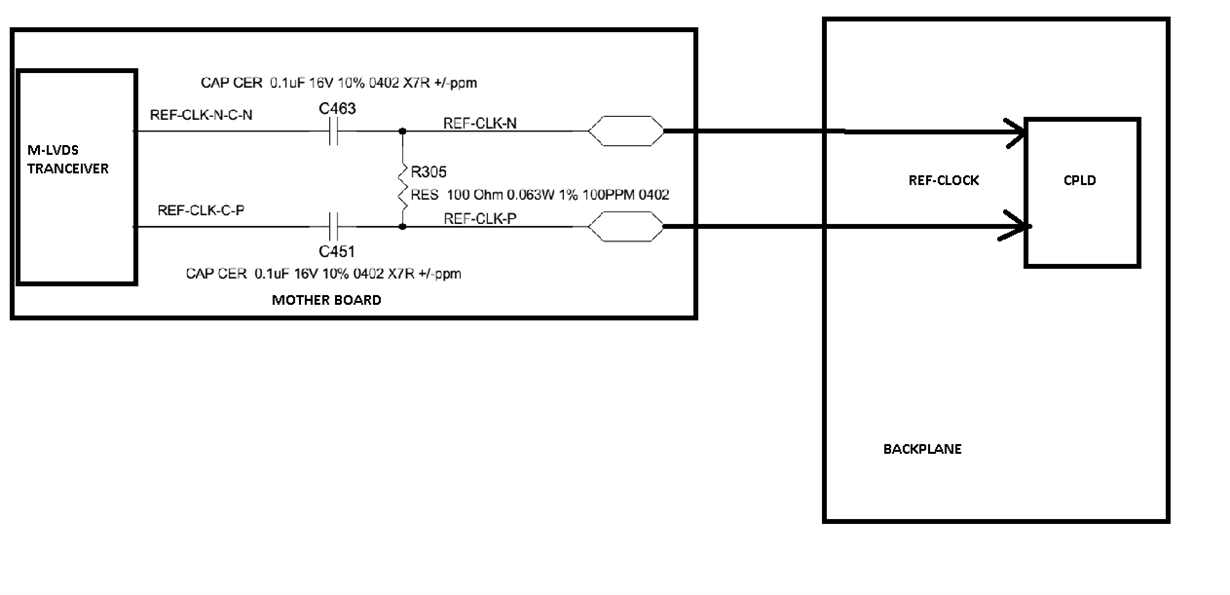

Iam designing a back plane for my system,In back plane i am using a CPLD for some logic realizations.the reference clock to the CPLD is decided route from the M-LVDS Driver (Point-point only).

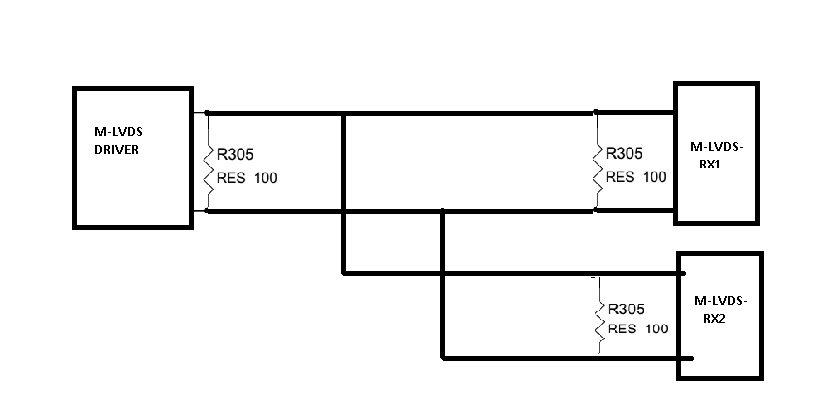

as shown in the figure M-LVDS Tranceiever side coupling capacitors and termination resistor are there,so i want to use it as a driver only,Whether in receiver side(cpld) can i provide the coupling capacitors and termination resistor(100 OHM).any issue will be there??? how can I design the path for the LVDS CLCOK from DS91M040 to CPLD. kINDLY SUPPORT ME.