Tool/software: TI C/C++ Compiler

Hi team, our team use SN65DSI86 as bridge IC to convert dual MIPI input to eDP output(resolution:3000*2000), we have some questions to ask,

Structure:

1.We can enter in SN65DSI86 BIST mode, but if we change to normal mode(input from dual MIPI signal), it can't work. Shoud we set some registers?

2.Dual MIPI has Sync Event,Sync Pulse,Burst setting, do we need to set some registers to match input mode for SN65DSI86?

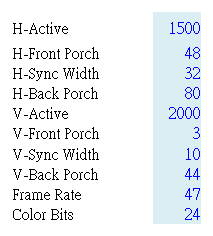

3 Here are the Panel timing and single MIPI input timing setting.

Panel Timing:

|

H-Active |

3000 |

|

H-Front Porch |

48 |

|

H-Sync Width |

32 |

|

H-Back Porch |

80 |

|

V-Active |

2000 |

|

V-Front Porch |

3 |

|

V-Sync Width |

10 |

|

V-Back Porch |

44 |

|

Frame Rate |

47 |

|

Color Bits |

24 |

single MIPI input timing setting: