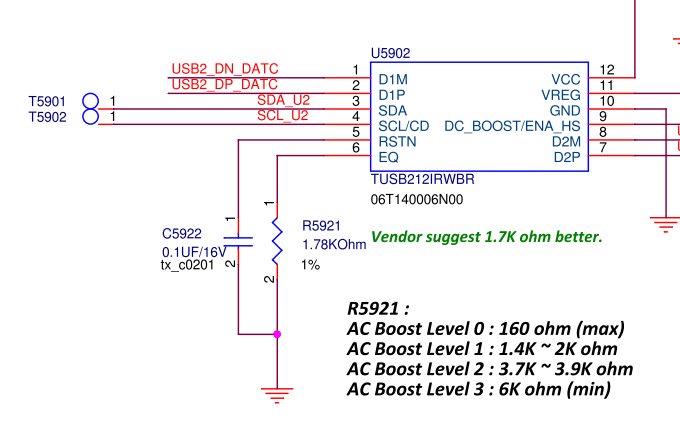

Part Number: TUSB212

Hi Sirs,

Sorry to bother you.

We've received the DVT MB (with TUSB212).

Althoughi DVT MB pass the USB2.0 test, but the jitter is worse than EVT.

Is there any way to improve the jitter through TUSB212?

Here is the U2 margin pass eye diagram for you to reference.

For jitter issue, may we lower the AC boost level to lower the jitter?

Update-

We find change to high level of ac boost will let jitter be more obviously. If enhanced dc & ac boost level to max, can have more margin, but will also reduce V-swing tolerance.

Due to can't find any emphasis tuning option, do you have other ideas for this ?

Fig-1. DC boost = L ; AC boost = level 1 (default)

Fig-2. DC boost = L ; AC boost = level 3

Fig-3. DC boost = H ; AC boost = level 0

Fig-4. DC boost = H ; AC boost = level 3

Fig-5. DC boost = L ; AC boost = level 0

(Wait for testing …)