Other Parts Discussed in Thread: DS80PCI810

Hi Team,

DS80PCI800 used on PCI-E riser card applications

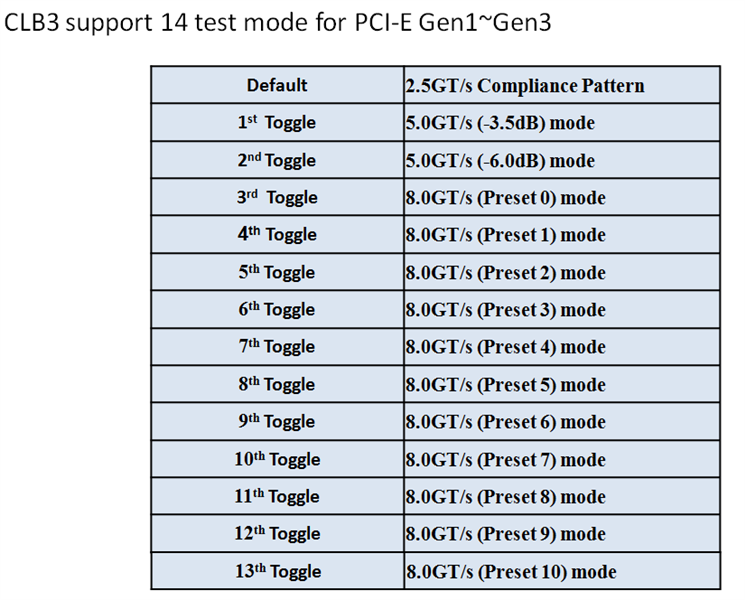

When testing the eye diagram and found that PCI-E GEN1 can pass but GEN3 can't pass.

Please refer attached files and help how to adjust the signal to pass GEN3.

Measure the results of PCI-E signal measurements.

Attachment instructions:

Original P0_Math1.html --> Original profile

Original P10_Math1.html --> Original profile

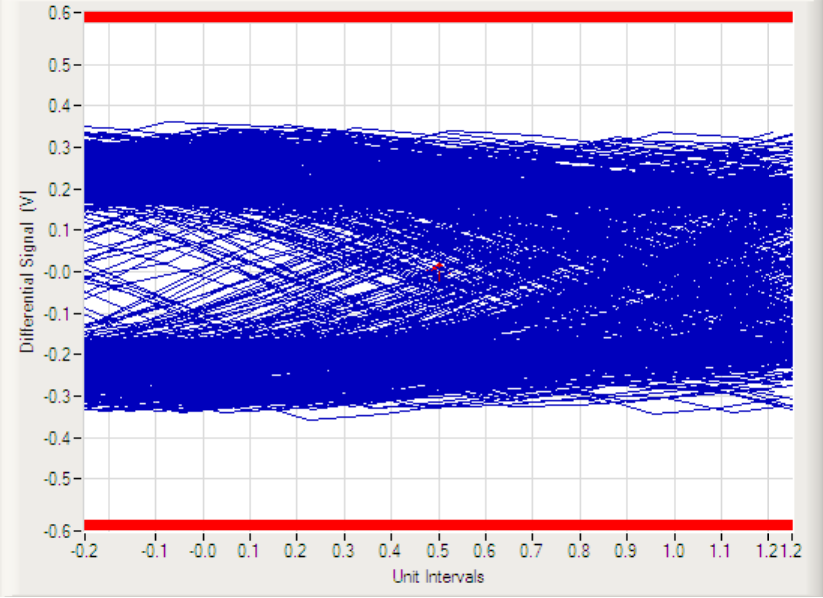

P0 failed eye diagram

P10 failure eye diagram

Adjust EQA1/EQB1=0, EQA0/EQB0=0 to set the result after measurement.

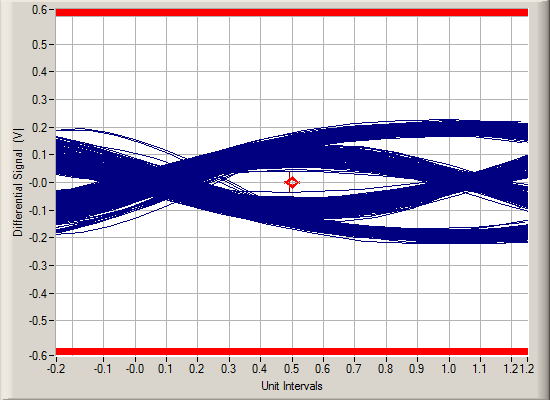

PCIE GEN3 Preset0 mode test eye have open

PCIE GEN3 Preset10 mode test still eye closed

Attachment instructions:

L0P0_Math1.html & L0P0_Math1.html --> Modified profile

Please help how to adjust the signal can pass GEN3.

thanks

Kevin

<html><body><h1> Results for c:\Users\Tek_Local_Admin\Desktop\Gary\CB-1816 A1\CN28\L7\l7\L0P0_Math1 </hs1><hr><p><p><p><font size=4><b><i> Sigtest: </i><font size=3><ul><li>Overall Sigtest Result:<font color=#6633CC> Pass! </font><p><li> Mean Unit Interval (ps): 125.000286<p><li> Min Time Between Crossovers (ps): 84.514544 <br><p><li> Data Rate (Gb/s): 7.999982 <br><p><li> Max Peak to Peak Jitter: 65.796315 ps<br><p><li> Total Jitter at BER of 10E-12: 68.069418 ps<br><font color=#6633CC> Total Jitter at BER of 10E-12 Passes Sigtest Limits! </font><p><li> Minimum eye width: 56.930582 ps<br><p><li> Deterministic Jitter Delta-Delta: 44.664186 ps<br><font color=#6633CC> Deterministic Jitter Delta-Delta Passes Sigtest Limits! </font><p><li> Random Jitter (RMS): 1.664668 ps<br><font color=#6633CC> Random Jitter (RMS) Passes Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage: -0.219711 volts<br><font color=#6633CC> Minimum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Transition Eye Voltage: 0.224105 volts<br><font color=#6633CC> Maximum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage: -0.23286 volts<br><font color=#6633CC> Minimum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Non Transition Eye Voltage: 0.235951 volts<br><font color=#6633CC> Maximum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Composit Eye Height: 0.075554<p><li> Composit Eye Location: 0.492<br><font color=#6633CC> Composit Eye Height Passes Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Above Eye: 0.018971 volts<br><font color=#6633CC> Minimum Transition Eye Voltage Margin Above Eye Passes Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Below Eye: -0.016388 volts<br><font color=#6633CC> Minimum Transition Eye Voltage Margin Below Eye Passes Sigtest Limits! </font><p><li> Minimum Transition Eye Height: 0.081358 volts<br> <p><li> Minimum Non Transition Eye Voltage Margin Above Eye: 0.070741 volts<br><font color=#6633CC> Minimum Non Transition Eye Voltage Margin Above Eye Passes Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage Margin Below Eye: -0.074669 volts<br><font color=#6633CC> Minimum Non Transition Eye Voltage Margin Below Eye Passes Sigtest Limits! </font><p><li> Minimum Non Transition Eye Height: 0.19141 volts<br> <br></ul><hr><p><i>Worst Non Transition Signal Eye</i><p><img src=".\L0P0_Math1Eye.png"></body></html> <br></ul><hr><p><i>Worst Transition Signal Eye</i><p><img src=".\L0P0_Math1TransitionEye.png"></body></html></font><p>TEMPLATE FILE SETTINGS<p><li> Template File: PCIE_3_0_SYS \ PCIE_3_8GB_CEM_DUAL_PORT<p><li> Nominal Data Rate (bits/sec): 8000000000.0<p><li> Target Unit Interval (s): 1.25e-010<p><li> Minimum Time Allowed Between Crossovers (s): 7.5e-011<p><li> Minimum Data For Testing (UI): 200<p><li> Ambiguous UI Resolution Method: EYE_AMBIGUOUS_NONE (0)<p><li> Tj@E-12 Peak to Peak Jitter Limit (s): 8.375e-011<p><li> Rj (RMS) Jitter Limit (s): 3.0e-012<p><li> CTLE equalization index = 7<p><li> DFE equalization: Tap 1 = -5.311185, Tap 2 unused<p><li> Compliance pattern preset = 0<p><li> Compliance pattern lane = 0<p>Sigtest Version: 3.2.11

<html><body><h1> Results for c:\Users\Tek_Local_Admin\Desktop\Gary\CB-1816 A1\CN28\L7\l7\L0P10_Math1 </hs1><hr><p><p><p><font size=4><b><i> Sigtest: </i><font size=3><ul><li>Overall Sigtest Result:<font color=#CC0033> Fail! </font><p><li> Mean Unit Interval (ps): 125.000314<p><li> Min Time Between Crossovers (ps): 93.304251 <br><p><li> Data Rate (Gb/s): 7.99998 <br><p><li> Max Peak to Peak Jitter: 1172.973743 ps<br><p><li> Total Jitter at BER of 10E-12: 2085.959448 ps<br><font color=#CC0033> Total Jitter at BER of 10E-12 Fails Sigtest Limits! </font><p><li> Minimum eye width: -1960.959448 ps<br><p><li> Deterministic Jitter Delta-Delta: -679.481091 ps<br><font color=#6633CC> Deterministic Jitter Delta-Delta Passes Sigtest Limits! </font><p><li> Random Jitter (RMS): 196.688516 ps<br><font color=#CC0033> Random Jitter (RMS) Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage: -0.204667 volts<br><font color=#6633CC> Minimum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Transition Eye Voltage: 0.20721 volts<br><font color=#6633CC> Maximum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage: -0.212364 volts<br><font color=#6633CC> Minimum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Non Transition Eye Voltage: 0.213556 volts<br><font color=#6633CC> Maximum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Composit Eye Height: 9.566975e-007<p><li> Composit Eye Location: 0.5<br><font color=#CC0033> Composit Eye Height Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Above Eye: -0.023 volts<br><font color=#CC0033> Minimum Transition Eye Voltage Margin Above Eye Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Below Eye: 0.023 volts<br><font color=#CC0033> Minimum Transition Eye Voltage Margin Below Eye Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Height: 0.0 volts<br> <p><li> Minimum Non Transition Eye Voltage Margin Above Eye: -0.023 volts<br><font color=#CC0033> Minimum Non Transition Eye Voltage Margin Above Eye Fails Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage Margin Below Eye: 0.023 volts<br><font color=#CC0033> Minimum Non Transition Eye Voltage Margin Below Eye Fails Sigtest Limits! </font><p><li> Minimum Non Transition Eye Height: 0.0 volts<br> <br></ul><hr><p><i>Worst Non Transition Signal Eye</i><p><img src=".\L0P10_Math1Eye.png"></body></html> <br></ul><hr><p><i>Worst Transition Signal Eye</i><p><img src=".\L0P10_Math1TransitionEye.png"></body></html></font><p>TEMPLATE FILE SETTINGS<p><li> Template File: PCIE_3_0_SYS \ PCIE_3_8GB_CEM_DUAL_PORT<p><li> Nominal Data Rate (bits/sec): 8000000000.0<p><li> Target Unit Interval (s): 1.25e-010<p><li> Minimum Time Allowed Between Crossovers (s): 7.5e-011<p><li> Minimum Data For Testing (UI): 200<p><li> Ambiguous UI Resolution Method: EYE_AMBIGUOUS_NONE (0)<p><li> Tj@E-12 Peak to Peak Jitter Limit (s): 8.375e-011<p><li> Rj (RMS) Jitter Limit (s): 3.0e-012<p><li> CTLE equalization index = 1<p><li> DFE equalization: Tap 1 = -10.080624, Tap 2 unused<p><li> Compliance pattern preset = 10<p><li> Compliance pattern lane = 0<p>Sigtest Version: 3.2.11

<html><body><h1> Results for c:\Users\Tek_Local_Admin\Desktop\Gary\CB-1816 A1\CN28\L0\P0_Math1 </hs1><hr><p><p><p><font size=4><b><i> Sigtest: </i><font size=3><ul><li>Overall Sigtest Result:<font color=#CC0033> Fail! </font><p><li> Mean Unit Interval (ps): 125.000348<p><li> Min Time Between Crossovers (ps): 96.710924 <br><p><li> Data Rate (Gb/s): 7.999978 <br><p><li> Max Peak to Peak Jitter: 284.311916 ps<br><p><li> Total Jitter at BER of 10E-12: 359.177952 ps<br><font color=#CC0033> Total Jitter at BER of 10E-12 Fails Sigtest Limits! </font><p><li> Minimum eye width: -234.177952 ps<br><p><li> Deterministic Jitter Delta-Delta: 167.957506 ps<br><font color=#6633CC> Deterministic Jitter Delta-Delta Passes Sigtest Limits! </font><p><li> Random Jitter (RMS): 13.600316 ps<br><font color=#CC0033> Random Jitter (RMS) Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage: -0.343506 volts<br><font color=#6633CC> Minimum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Transition Eye Voltage: 0.341976 volts<br><font color=#6633CC> Maximum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage: -0.358157 volts<br><font color=#6633CC> Minimum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Non Transition Eye Voltage: 0.361277 volts<br><font color=#6633CC> Maximum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Composit Eye Height: 1.672845e-005<p><li> Composit Eye Location: 0.5<br><font color=#CC0033> Composit Eye Height Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Above Eye: -0.022994 volts<br><font color=#CC0033> Minimum Transition Eye Voltage Margin Above Eye Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Below Eye: 0.023006 volts<br><font color=#CC0033> Minimum Transition Eye Voltage Margin Below Eye Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Height: 0.0 volts<br> <p><li> Minimum Non Transition Eye Voltage Margin Above Eye: -0.022984 volts<br><font color=#CC0033> Minimum Non Transition Eye Voltage Margin Above Eye Fails Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage Margin Below Eye: 0.023016 volts<br><font color=#CC0033> Minimum Non Transition Eye Voltage Margin Below Eye Fails Sigtest Limits! </font><p><li> Minimum Non Transition Eye Height: 0.0 volts<br> <br></ul><hr><p><i>Worst Non Transition Signal Eye</i><p><img src=".\P0_Math1Eye.png"></body></html> <br></ul><hr><p><i>Worst Transition Signal Eye</i><p><img src=".\P0_Math1TransitionEye.png"></body></html></font><p>TEMPLATE FILE SETTINGS<p><li> Template File: PCIE_3_0_SYS \ PCIE_3_8GB_CEM_DUAL_PORT<p><li> Nominal Data Rate (bits/sec): 8000000000.0<p><li> Target Unit Interval (s): 1.25e-010<p><li> Minimum Time Allowed Between Crossovers (s): 7.5e-011<p><li> Minimum Data For Testing (UI): 200<p><li> Ambiguous UI Resolution Method: EYE_AMBIGUOUS_NONE (0)<p><li> Tj@E-12 Peak to Peak Jitter Limit (s): 8.375e-011<p><li> Rj (RMS) Jitter Limit (s): 3.0e-012<p><li> CTLE equalization index = 7<p><li> DFE equalization: Tap 1 = -25.393572, Tap 2 unused<p><li> Compliance pattern preset = 0<p><li> Compliance pattern lane = 0<p>Sigtest Version: 3.2.11

<html><body><h1> Results for c:\Users\Tek_Local_Admin\Desktop\Gary\CB-1816 A1\CN28\L0\P10_Math1 </hs1><hr><p><p><p><font size=4><b><i> Sigtest: </i><font size=3><ul><li>Overall Sigtest Result:<font color=#CC0033> Fail! </font><p><li> Mean Unit Interval (ps): 125.000335<p><li> Min Time Between Crossovers (ps): 100.790799 <br><p><li> Data Rate (Gb/s): 7.999979 <br><p><li> Max Peak to Peak Jitter: 775.24782 ps<br><p><li> Total Jitter at BER of 10E-12: 1416.638235 ps<br><font color=#CC0033> Total Jitter at BER of 10E-12 Fails Sigtest Limits! </font><p><li> Minimum eye width: -1291.638235 ps<br><p><li> Deterministic Jitter Delta-Delta: -382.235949 ps<br><font color=#6633CC> Deterministic Jitter Delta-Delta Passes Sigtest Limits! </font><p><li> Random Jitter (RMS): 127.942687 ps<br><font color=#CC0033> Random Jitter (RMS) Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage: -0.337965 volts<br><font color=#6633CC> Minimum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Transition Eye Voltage: 0.334648 volts<br><font color=#6633CC> Maximum Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage: -0.350893 volts<br><font color=#6633CC> Minimum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Maximum Non Transition Eye Voltage: 0.355698 volts<br><font color=#6633CC> Maximum Non Transition Eye Voltage Passes Sigtest Limits! </font><p><li> Composit Eye Height: 2.120859e-006<p><li> Composit Eye Location: 0.5<br><font color=#CC0033> Composit Eye Height Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Above Eye: -0.023001 volts<br><font color=#CC0033> Minimum Transition Eye Voltage Margin Above Eye Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Voltage Margin Below Eye: 0.022999 volts<br><font color=#CC0033> Minimum Transition Eye Voltage Margin Below Eye Fails Sigtest Limits! </font><p><li> Minimum Transition Eye Height: 0.0 volts<br> <p><li> Minimum Non Transition Eye Voltage Margin Above Eye: -0.023 volts<br><font color=#CC0033> Minimum Non Transition Eye Voltage Margin Above Eye Fails Sigtest Limits! </font><p><li> Minimum Non Transition Eye Voltage Margin Below Eye: 0.023 volts<br><font color=#CC0033> Minimum Non Transition Eye Voltage Margin Below Eye Fails Sigtest Limits! </font><p><li> Minimum Non Transition Eye Height: 0.0 volts<br> <br></ul><hr><p><i>Worst Non Transition Signal Eye</i><p><img src=".\P10_Math1Eye.png"></body></html> <br></ul><hr><p><i>Worst Transition Signal Eye</i><p><img src=".\P10_Math1TransitionEye.png"></body></html></font><p>TEMPLATE FILE SETTINGS<p><li> Template File: PCIE_3_0_SYS \ PCIE_3_8GB_CEM_DUAL_PORT<p><li> Nominal Data Rate (bits/sec): 8000000000.0<p><li> Target Unit Interval (s): 1.25e-010<p><li> Minimum Time Allowed Between Crossovers (s): 7.5e-011<p><li> Minimum Data For Testing (UI): 200<p><li> Ambiguous UI Resolution Method: EYE_AMBIGUOUS_NONE (0)<p><li> Tj@E-12 Peak to Peak Jitter Limit (s): 8.375e-011<p><li> Rj (RMS) Jitter Limit (s): 3.0e-012<p><li> CTLE equalization index = 7<p><li> DFE equalization: Tap 1 = -28.984696, Tap 2 unused<p><li> Compliance pattern preset = 10<p><li> Compliance pattern lane = 0<p>Sigtest Version: 3.2.11